Applets

contents

visual index

introduction

introduction std_logic_1164

std_logic_1164 gatelevel circuits

gatelevel circuits delay models

delay models flipflops

flipflops adders and arithm...

adders and arithm... counters

counters LFSR and selftest

LFSR and selftest memories

memories programmable logic

programmable logic state-machine editor

state-machine editor misc. demos

misc. demos I/O and displays

I/O and displays DCF-77 clock

DCF-77 clock relays (switch-le...

relays (switch-le... CMOS circuits (sw...

CMOS circuits (sw... RTLIB logic

RTLIB logic RTLIB registers

RTLIB registers Prima processor

Prima processor D*CORE

D*CORE MicroJava

MicroJava Pic16 cosimulation

Pic16 cosimulation Mips R3000 cosimu...

Mips R3000 cosimu... Intel MCS4 (i4004)

Intel MCS4 (i4004) image processing ...

image processing ... [Sch04] Codeumsetzer

[Sch04] Codeumsetzer [Sch04] Addierer

[Sch04] Addierer [Sch04] Flipflops

[Sch04] Flipflops [Sch04] Schaltwerke

[Sch04] Schaltwerke [Sch04] RALU, Min...

[Sch04] RALU, Min... [Fer05] State-Mac...

[Fer05] State-Mac... [Fer05] PIC16F84/...

[Fer05] PIC16F84/... [Fer05] Miscellan...

[Fer05] Miscellan... [Fer05] Femtojava

[Fer05] Femtojava

adder

adder

factorial

factorial

calculator

calculator

Multicycle F...

Multicycle F...

Bubblesort

Bubblesort

Insertion-sort

Insertion-sort

Quicksort

Quicksort

Pipelined Fe...

Pipelined Fe...

quicksort (p...

quicksort (p... FreeTTS

FreeTTSThe Low-Power Java processor uses the forwarding technique, which brings an advantage when comparing to RISC like processors: in instructions that manipulate the stack, the operands forwarded to earlier stages will not be used anymore. As a consequence, there is no need to write back these operands to the stack. The result is the reduction on the power consumption, because the number of writes in the stack is reduced.

Please look at the following to learn more about FemtoJAVA pipeline [1], Sashimi Project [3] and CACO-PS [2] power estimation tool from Universidade Federal do Rio Grande do SUL (UFRGS), Brazil, head by Luigi Carro;

[1] CARRO, L. ; BECK FILHO, A C S . Low Power Java Processor for Embedded Applications. In: IFIP VLSI-SOC, 2003, Darmstadt. IFIP WG 105 Proceedings, 2003. p. 239-244. [2] BECK FILHO, Antonio Carlos ; MATTOS, Julio ; WAGNER, Flavio ; CARRO, L. . CACO PS - A General Purpose Cycle-accurate Configurable Power Simulator. In: 16th Symposium on Integrated Circuits and Systems Design, 2003, São Paulo. Proceedings. Los Alamitos : IEEE Computer Society Press, 2003. v. 1. p. 349-354. [3] ITO, S., CARRO, L., JACOBI, R. Sashimi and FemtoJava: making Java work for microcontroller applications. IEEE Design & Test of Computers. Estados Unidos: , p.100 - 110, 2001. This circuit was originally generated on CACO-PS Format (FJA FILE) [2]. CACO-PS is A General Purpose Cycle-accurate Configurable Power Simulator written on C, from UFRGS, Brazil. A FJA file is a structural format. Each component on CACO-PS has a C function to describe its behavior. A parser to converter FJA on HDS was written by Alisson Garcia and Ricardo Ferreira. Each C behavior description was encapsulated on Java file to generate a HADES component.Usage:

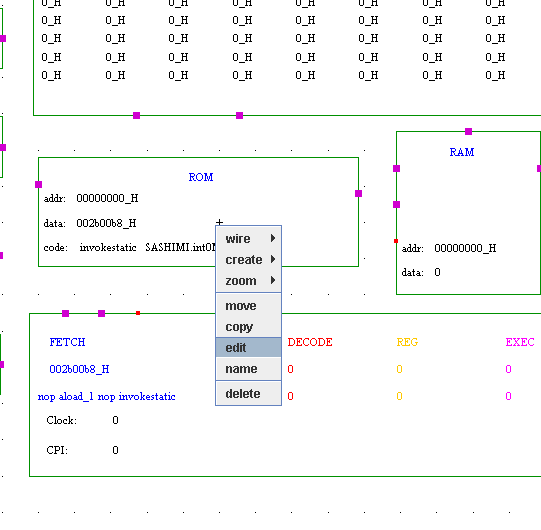

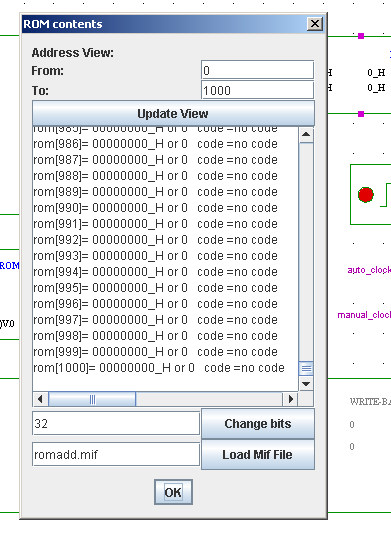

Please wait until the applet is fully loaded. As explained above, the schematics was generated automatically from the synthesized processor description. While there are a lot of components, all interesting components are in the top left corner. Therefore, please use the 'zoom region' to first zoom into the top-left corner of the schematics before running the simulation. You might also want to open the applet in an external window (popup > window > open external window) to enlarge the window. Then use the popup-menu ('edit') on the ROM component to open the window with preferences. The default (romadd.mif) its a simple program based on the following code:

int a,b,c; a = 5; b = 7; c = a + b;

If you want to change the program, you can put these mif files in the box,

then click on Load Mif file:

romSortBubble.mif -> Bubble Sort Code

romSortInsert.mif -> Sort Insert Code

romSortQuick.mif -> Quick Sort Code

romSortSelect.mif -> Select Sort Code

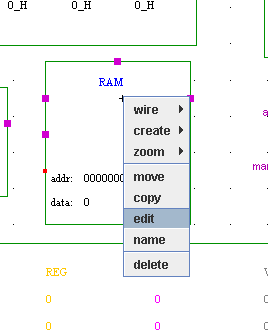

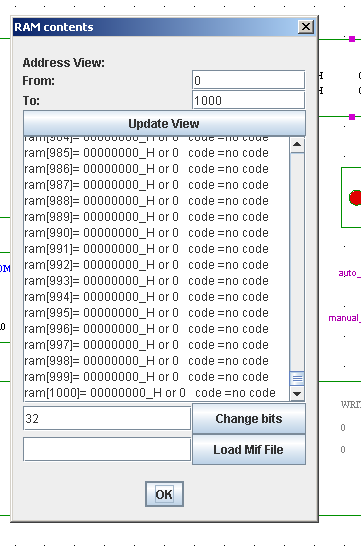

If you changed the default mif on the ROM,

you will need to change the RAM component.

Use the popup-menu ('edit') on the RAM component

to open the window with the preferences.

If you want to change the program, you can put these mif files in the box,

then click on Load Mif file:

romSortBubble.mif -> Bubble Sort Code

romSortInsert.mif -> Sort Insert Code

romSortQuick.mif -> Quick Sort Code

romSortSelect.mif -> Select Sort Code

If you changed the default mif on the ROM,

you will need to change the RAM component.

Use the popup-menu ('edit') on the RAM component

to open the window with the preferences.

ramSortBubble.mif -> If you chose the Bubble Sort Code

ramSortInsert.mif -> If you chose the Sort Insert Code

ramSortQuick.mif -> If you chose the Quick Sort Code

ramSortSelect.mif -> If you chose the Select Sort Code

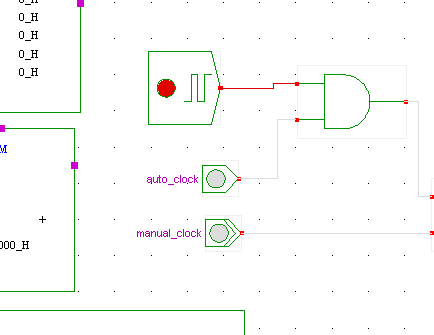

Now, you can start the simulation. If you want that the simulation runs automatic, just turn on the auto_clock, otherwise, you can control the clocks just clicking in manual_clock button.

The processor finishes the default code in 45 cycles.

Sort codes needs about 2000 cycles to finish.

During the simulation, the Cycle per Instrution (CPI),

Clock Cycles, Instruction Count can be measured.

Thanks to HADES graphical interface, the pipeline flow can be also monitored.

The instrumentation is a useful resource to better understanding

the processor skills.

Learnning and writing a simula

tor could be a complex task to be developed during a undergraduate course.

Due the high complexity, [Reddi,2004] have shown that

computer architecture education should handle program behavior and

real workload by using effective tools. Our approach is similar,

however we use a object-oriented language.

The result can be found at the ram memory. For the default code,

the result is placed at position 19. For the Sort codes,

the vector generally start at position 20 (except for the ramQuickSort.mif).

The processor finishes the default code in 45 cycles.

Sort codes needs about 2000 cycles to finish.

During the simulation, the Cycle per Instrution (CPI),

Clock Cycles, Instruction Count can be measured.

Thanks to HADES graphical interface, the pipeline flow can be also monitored.

The instrumentation is a useful resource to better understanding

the processor skills.

Learnning and writing a simula

tor could be a complex task to be developed during a undergraduate course.

Due the high complexity, [Reddi,2004] have shown that

computer architecture education should handle program behavior and

real workload by using effective tools. Our approach is similar,

however we use a object-oriented language.

The result can be found at the ram memory. For the default code,

the result is placed at position 19. For the Sort codes,

the vector generally start at position 20 (except for the ramQuickSort.mif).