Applets

contents

visual index

introduction

introduction std_logic_1164

std_logic_1164 gatelevel circuits

gatelevel circuits delay models

delay models flipflops

flipflops adders and arithm...

adders and arithm... counters

counters LFSR and selftest

LFSR and selftest memories

memories programmable logic

programmable logic state-machine editor

state-machine editor misc. demos

misc. demos I/O and displays

I/O and displays DCF-77 clock

DCF-77 clock relays (switch-le...

relays (switch-le... CMOS circuits (sw...

CMOS circuits (sw... RTLIB logic

RTLIB logic RTLIB registers

RTLIB registers Prima processor

Prima processor D*CORE

D*CORE MicroJava

MicroJava Pic16 cosimulation

Pic16 cosimulation Mips R3000 cosimu...

Mips R3000 cosimu... Intel MCS4 (i4004)

Intel MCS4 (i4004) image processing ...

image processing ... [Sch04] Codeumsetzer

[Sch04] Codeumsetzer [Sch04] Addierer

[Sch04] Addierer [Sch04] Flipflops

[Sch04] Flipflops [Sch04] Schaltwerke

[Sch04] Schaltwerke [Sch04] RALU, Min...

[Sch04] RALU, Min... [Fer05] State-Mac...

[Fer05] State-Mac... [Fer05] PIC16F84/...

[Fer05] PIC16F84/... [Fer05] Miscellan...

[Fer05] Miscellan... [Fer05] Femtojava

[Fer05] Femtojava

adder

adder

factorial

factorial

calculator

calculator

Multicycle F...

Multicycle F...

Bubblesort

Bubblesort

Insertion-sort

Insertion-sort

Quicksort

Quicksort

Pipelined Fe...

Pipelined Fe...

quicksort (p...

quicksort (p... FreeTTS

FreeTTSThe applet directly loads the quicksort algorithm into the program ROM and some initial (unsorted) data into the main memory RAM. Again, the binary memory data dumps (mif files for RAM and ROM) were generated using the Sashimi Tool.

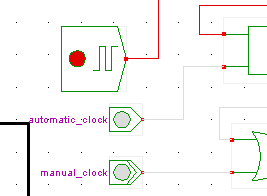

Now, you can start the simulation. If you want that the simulation runs automatic, just turn on the auto_clock, otherwise, you can control the clocks just clicking in manual_clock button.

The sort program needs about 5800 cicles to finish.

The result can be found in the RAM memory, starting at address 20.

The sort program needs about 5800 cicles to finish.

The result can be found in the RAM memory, starting at address 20.