welcome

welcome news

news gate-level

gate-level rtlib

rtlib cosimulation

cosimulation browser

browser waveforms

waveforms scripting

scripting documentation

documentation download

download webstart

webstart gallery

gallery links

links about

aboutApplets

contents

contents visual index

visual index usage

usage FAQ

FAQ feedback

feedback license

license

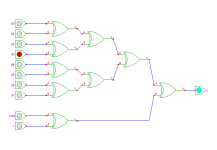

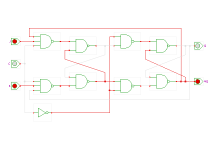

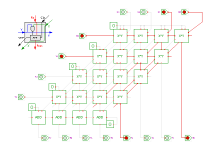

Gate-level components

The Hades framework includes a large library of simulation models for digital systems. All gate-level simulation models are based on the industry-standard VHDL std_logic_1164 multilevel logic system. While std_logic_1164 is slightly more complex than the simple 01X- or 01XZ-logic models, the option to model bus systems with floating ('Z') and weak ('H') values is a clear advantage. The use of std_logic_1164 also means that students will already be trained in a multilevel logic model from the beginnning.The thumbnails below show three simple circuits built from Hades gate-level simulation models. Check the applet collection for the interactive versions of these circuits. From left to right:

- parity generator (8+2 bits).

- JK-flipflop.

- array multiplier (4x4 bits).

Additional visualization aids are provided in the schematics editor to help understanding the behaviour of the circuits. For example, the dominant cyan and magenta colors used for the 'U' and 'X' logic values allow to identify un-initialized signals 'at a glance':

- 'glow-mode' animation with colors based on the current logic value of a signal.

- special 'glow-mode' colors for undefined ('U', 'X') or tri-stated ('Z') buses.

- context-tooltips provide additional information about signals and components (e.g. clock-generator period, gate-delays, number of events).

- 'real-time' simulation mode slows down the simulator to visualize circuit timing (e.g. propagation delays).

- component property-sheets allow you to set component properties while the simulation is running (e.g. timing parameters).

So far, the Hades simulation model library includes:

- all basic gates with up to four inputs (buffer, inverter, AND, OR, NAND, NOR, XOR).

- complex gates (AOI and OAI).

- multiplexers and tri-state buffers.

- all standard latches and flipflops.

- a variety of interactive switches and displays.

- variants of all the above with DIN-style (German) symbols.

- TTL-series combinational components (e.g. 7400/7449/74154).

- TTL-series arithmetic (e.g. 7483/74181/74182).

- TTL-series registers and counters (e.g. 7447/74390/74590).

- registers and memories (RAM, ROM, e.g. 74219, 6116).

- linear-feedback shift-registers.

- configurable RS-232 terminal.

- text-mode and graphics LC displays.

- subdesigns (can be nested to arbitrary depth).

- a stimuli-generator component.

- counters and detectors (e.g. hazard-detectors).

- a state-machine editor.

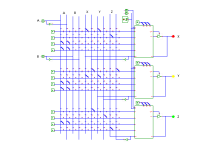

The following image shows the demonstration of a programmable GAL ("generic array logic") circuit. Three output cells are used, each of which provides four AND-gates (terms) with five inputs (A,B,X,Y,Z). Special interactive switches are used to model the fuses; simply clicking a switch changes the fuse status (intact/blown) and immediately updates the simulation. Click the thumbnail below for a larger screenshot, or click here for the interactive applet version of the GAL traffic light controller demo: