PalCo

Digitaler PAL-Videosignal-Encoder in einem FPGA

DSP'99Der rein digitale PAL-Encoder enthält alle Signalverarbeitungskomponenten, die zur Erzeugnung eines PAL-Videosignals (FBAS = Farb-Bild-Austast-Signal) erforderlich sind. Der PAL-Encoder erzeugt aus YUV-Komponenten [8:4:4] das PAL-FBAS-Signal. Ein Timer erzeugt ein Interlaced-Synchronisationsschema und interne Steuersignale. Ein Sinus-Generator (DDS = Direkte Digital Synthese) erzeugt das PAL-Farbträgersignal (4,43381675 MHz) aus einem festen (grundsätzlich beliebig wählbaren) Taktsignal von derzeit 30 MHz. Schnelle Phasenumtastung ermöglicht die Auswahl von einer von vier möglichen Phasen (0°, 90°, +135°, -135°) die für das Burst-Signal (A/B) und für die QAM-Modulation (QAM = Quadratur - Amplituden - Modulation) der beiden Farbdifferenzsignale U und V zur Erzeugung des Chominanz-Signals C benötigt werden. Die Abtastfrequenz beträgt die Hälfte der Taktfrequenz (15 MHz). Ein Video-Mixer mischt das digitale Luminanz-Signal Y mit dem digitalen Chrominanz-Signal C und tastet die Schwarzschulter- Synchronisationssignale durch und liefert so ein digitales FBAS-Signal. Der implementierte PAL-Encoder hat folgende Blockstruktur:

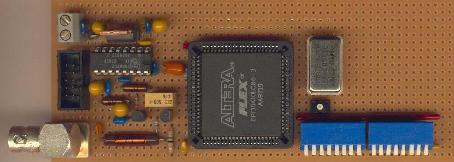

Die erstellte VHDL-Verhaltensbeschreibung des PAL-Encoders konnte leicht mit folgender FPGA-Prototyp-Platine validiert werden. Die Validierung mit Hilfe von VHDL-Simulationen erfordert sehr hohe Simulationszeiten (ca. 30 Minuten Simulationszeit für eine Bildsequenz von 0,16 Sekunden Echtzeit). Die Komponente YUV-DEMO erzeugt einen digitalen YUV-Datenstrom zur Darstellung auf einem Farbfernseher - die Luminanz wird dabei langsam variiert, so daß der von dem PAL-Encoder darstellbare YUV-Farbraum vollständig durchlaufen wird.

Das digitale FBAS-Signal des FPGA-Prototypen wird mit einem Video-DAC in ein analoges FBAS-Signal umgewandelt, das dann auf einem analogen PAL-Farbfernseher dargestellt werden kann. So kann das Ergebnis aller für den Schaltungsentwurf notwendigen numerischen Näherungen abschließend in seiner Gesamtheit auf der Systemebene bewertet werden.

Alle Komponenten der Schaltung wurden in VHDL beschrieben und simuliert. Der Entwurf ist im Rahmen des Promotionsvorhabens von Lars Larssson entstanden. Der digitale PAL-Encoder stellt ein Fallbeispiel für ein System dar, bei dessen funktionaler Validierung die Wechselwirkung mit der Systemumgebung eine ganz besonders wichtige Rolle spielt.

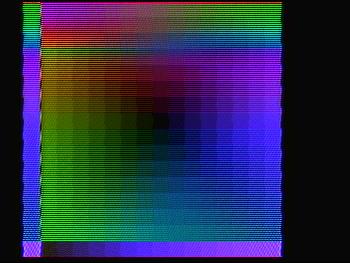

Das dargestellte Video-Bild ist das Ergebnis einer VHDL-Simulation des digitalen PAL-Encoders. Dabei ist Y = 0, U und V sind Funktionen von Zeile und Spalte. Das von der VHDL-Simulation gelieferte, digitale FBAS-Signal wurde dazu in eine Datei geschrieben. Mit einem digitalen PAL-Decoder, der als ausführbare Spezifikation (C-Programm) vorliegt, wurde ein Farbbild aus dem digitalen FBAS-Datenstrom der VHDL-Simulation extrahiert. Die Bildqualität ist bei der Darstellung auf einem realen TV besser. Das synthetisierbare VHDL-Modell des digitalen PAL-Encoders ist gegenüber der ausführbaren Spezifikation (C-Programm) des digitalen PAL-Encoders etwas vereinfacht, um in das kleine Prototyp-FPGA hinein zu passen. Der FPGA-Prototyp des digitalen PAL-Encoders läuft etwa 10000-mal schneller als die VHDL-Verhaltenssimulation. Mit dem digitalen PAL-Encoder-C-Programm wird eine Bildqualität wie von einer Videokamera erreicht, was mit Hilfe der bidirektionalen Videosignalschnittstelle VidTrans gezeigt werden kann.

technische Information

| FPGA | 1 x Altera FPGA Typ EPF10K10LC84-3 |

| TIMER | H-Sync, V-Sync, Burst-Gate, Schwarz-Schulter, interne Steuersignale |

| DDS | Digitaler Sinus-Generator fü PAL-Farbträgersignal (4,433.618.75 MHz) |

| QAM | Modulation : C = U*sin(wt) + V*cos(wt) |

| MIXER | FBAS = ( Y + C ) & Dunkeltastung & A/B-Burst & Composite-Sync |

| Gatteräquivalente | ~ 6k |

| Pads | 84 |

| Video-DAC | Philips TDA8702 |

| Systemtaktfrequenz | 30 MHz |

| Abtastfrequenz | 15 MHz |

| YUV [8:4:4] | Y[8 Bit, unsigned] : U[4 Bit, signed] : V[4 Bit, signed] |

| digitales FBAS-Signal | 8 Bit [unsigned] |