welcome

welcome news

news gate-level

gate-level rtlib

rtlib cosimulation

cosimulation browser

browser waveforms

waveforms scripting

scripting documentation

documentation download

download webstart

webstart gallery

gallery links

links about

aboutApplets

contents

contents visual index

visual index usage

usage FAQ

FAQ feedback

feedback license

license

A library of register-transfer-level components

Besides the standard gate-level simulation components like gates and flipflops, the Hades framework also provides an extensive library (called rtlib) of user-configurable register-transfer-level simulation components. While the standard gates and flipflops are based on the std_logic_1164 multilevel logic system, the rtlib multiple-bit simulation components are based on the std_logic_vector model and its arithmetic and logic functions. Naturally, one can easily mix standard and rtlib components (std_logic_1164 and std_logic_vector).Click the thumbnails below to see larger screenshots of three example circuits based on rtlib components. Check the applet collection for the interactive versions of the circuits. From left to right:

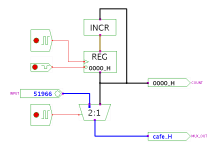

- rtlib demo with input-switches, incrementer, multiplexer, register.

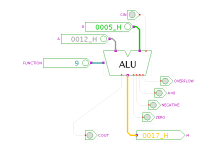

- user-configurable ALU.

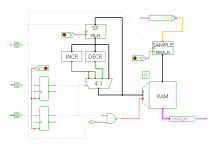

- stack-memory ('single-cycle clocked stack') based on a standard asynchronous RAM.

The rtlib library consists of the Java package hades.models.rtlib and its sub-packages like hades.models.rtlib.arith or hades.models.rtlib.memory. Most of the multi-bit arithmetic and logic functions are provided by the class hades.models.StdLogicVector, while class hades.signals.SignalStdLogicVector is used for multi-bit signals. The current implementation is limited to buses at most 63-bit wide, due to its use of a very compact storage scheme.

Additional visualization aids are provided in the schematics editor to help understanding the behaviour of register-transfer level circuits:

- 'glow-mode' animation with colors based on the current numerical value of the bus signals.

- special 'glow-mode' colors for undefined ('U', 'X') or tri-stated ('Z') buses.

- several components display their current value numerically (e.g. registers and the 'OpinVector' output connectors).

- user-selected number formats: decimal, hexadecimal, or binary.

- context-sensitive tooltips that display a component's current parameters.

- standard property-sheets to select component parameters for simple components (e.g. incrementer).

- custom user-interface windows for complex simulation models (e.g. memory-editors with integrated disassembler).

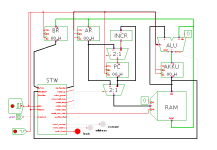

Naturally, rtlib components can be used to construct more complex circuits. For example, click the following thumbnail to see a larger screenshot of our PRIMA processor ("primitive machine"), or click here to open the interactive applet version. The processor is kept as simple as possible, to teach the basics of the von-Neumann machine paradigm. The 8-bit accumulator machine is built from just four registers (accumulator, program counter, instruction register, and address register), the ALU, one incrementer, two multiplexers, and the main memory: