## Rechnerarchitektur: ISA / Pipelining / Speicher

https://tams.informatik.uni-hamburg.de

#### Andreas Mäder

Universität Hamburg Fakultät für Mathematik, Informatik und Naturwissenschaften Fachbereich Informatik

Technische Aspekte Multimodaler Systeme

November 2020

Die folgenden Folien sind ein Auszug aus den Unterlagen der Vorlesung 64-613 Rechnerarchitekturen und Mikrosystemtechnik vom Wintersemester 2011/2012 und 64-040 Rechnerstrukturen und Betriebssysteme vom WS 2019/2020.

Das komplette Material findet sich auf den Web-Seiten unter https://tams.informatik.uni-hamburg.de/lectures/2011ws/vorlesung/ram, bzw. https://tams.informatik.uni-hamburg.de/lectures/2019ws/vorlesung/rsb

- ▶ D. Patterson, J. Hennessy: Computer Organization and Design

− The Hardware/Software Interface MIPS Edition [PH20]

- ► J. Hennessy, D. Patterson: *Computer architecture A quantitative approach* [HP17]

- ► A. Tanenbaum, T. Austin: Rechnerarchitektur Von der digitalen Logik zum Parallelrechner [TA14]

- ► W. Stallings: Computer Organization and Architecture –

Designing for Performance [Sta19]

- https://de.wikipedia.org und https://en.wikipedia.org

Rechnerarchitektui

#### 1. Rechnerarchitektur

Motivation von-Neumann Architektur Wie arbeitet ein Rechner?

- 2. Bewertung von Architekturen und Rechnersystemen

- 3. Instruction Set Architecture

- 4. Pipelining

- 5. Speicherhierarchie

Rechnerarchitektur - Motivation

Rechnerarchitektur

#### Definitionen

The term architecture is used here to describe the attributes of a system as seen by the programmer, i.e., the conceptual structure and functional behaviour, as distinct from the organization and data flow and control, the logical and the physical implementation. [Amdahl, Blaauw, Brooks]

The study of computer architecture is the study of the organization and interconnection of components of computer systems. Computer architects construct computers from basic building blocks such as memories, arithmetic units and buses.

Rechnerarchitektur - Motivation

From these building blocks the computer architect can construct anyone of a number of different types of computers, ranging from the smallest hand-held pocket-calculator to the largest ultra-fast super computer. The functional behaviour of the components of one computer are similar to that of any other computer, whether it be ultra-small or ultra-fast.

By this we mean that a memory performs the storage function, an adder does addition, and an input/output interface passes data from a processor to the outside world, regardless of the nature of the computer in which they are embedded. The major differences between computers lie in the way of the modules are connected together, and the way the computer system is controlled by the programs. In short, computer architecture is the discipline devoted to the design of highly specific and individual computers from a collection of common building blocks. [Stone]

Rechnerarchitektur - Motivation

Rechnerarchitektur

## Zwei Aspekte der Rechnerarchitektur

Operationsprinzip: das funktionelle Verhalten der Architektur

Befehlssatz

- = Programmierschnittstelle

- = ISA Instruction Set Architecture

- = Maschinenorganisation: Wie werden Befehle abgearbeitet?

2. Hardwarearchitektur: der strukturelle Aufbau des Rechnersystems

Mikroarchitektur

- Art und Anzahl der Hardware-Betriebsmittel + die Verbindungs- / Kommunikationseinrichtungen

- = (technische) Implementierung

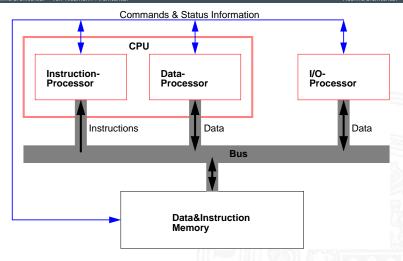

- ▶ J. Mauchly, J.P. Eckert, J. von-Neumann 1945

- ▶ abstrakte Maschine mit minimalem Hardwareaufwand

- die Struktur ist unabhängig von dem Problem, das durch Speicherinhalt (Programm) beschrieben wird

- Hardwarekomponenten

- zentrale Recheneinheit: CPU, (logisch) unterteilt in

- 1. Datenprozessor / Rechenwerk / Operationswerk

- 2. Befehlsprozessor / Leitwerk / Steuerwerk

- gemeinsamer Speicher für Programme und Daten

- fortlaufend adressiert

- ▶ Programme können wie Daten manipuliert werden

- ▶ Daten können als Programm ausgeführt werden

- ► Ein/Ausgabe-Einheit zur Anbindung peripherer Geräte

- ▶ Bussystem(e) verbinden diese Komponenten

## von-Neumann Architektur (cont.)

Rechnerarchitektur - von-Neumann Architektur

- ► Prozessor (CPU) = Steuerwerk + Operationswerk

- ► Steuerwerk: zwei zentrale Register

- ▶ Befehlszähler (program counter PC)

- ► Befehlsregister (instruction register IR)

- Operationswerk (Datenpfad, data-path)

- ► Rechenwerk (arithmetic-logic unit ALU)

- Universalregister (mind. 1 Akkumulator, typisch 8..64 Register)

- evtl. Register mit Spezialaufgaben

- ► Speicher (*memory*)

- ► Hauptspeicher/RAM: random-access memory

- ► Hauptspeicher/ROM: read-only memory zum Booten

- ► Externspeicher: Festplatten, CD/DVD, Magnetbänder

- ► Peripheriegeräte (Eingabe/Ausgabe, I/O)

Rechnerarchitektur - von-Neumann Architektur

- von-Neumann Konzept

- Programm als Sequenz elementarer Anweisungen (Befehle)

- als Bitvektoren im Speicher codiert

- Interpretation (Operanden, Befehle und Adressen) ergibt sich aus dem Kontext (der Adresse)

- zeitsequenzielle Ausführung der Instruktionen

Rechnerarchitektur

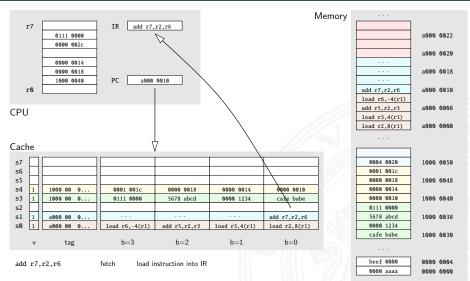

Rechnerarchitektur - Wie arbeitet ein Rechner?

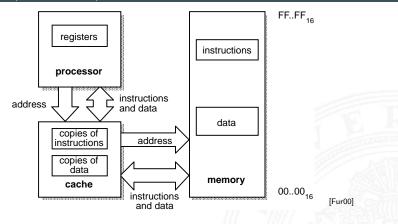

- "von-Neumann Flaschenhals": Zugriff auf Speicher

- ⇒ Erweiterungen aktueller Systeme

- ▶ parallele, statt sequenzieller Befehlsabarbeitung

⇒ Pipelining

- ▶ mehrere Ausführungseinheiten

⇒ superskalare Prozessoren, Mehrkern-Architekturen

- ▶ dynamisch veränderte Abarbeitungsreihenfolge ⇒ "out-of-order execution"

- ▶ getrennte Daten- und Instruktionsspeicher ⇒ Harvard-Architektur

- ► Speicherhierarchie, Caches etc.

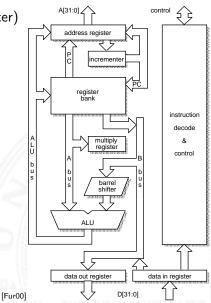

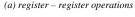

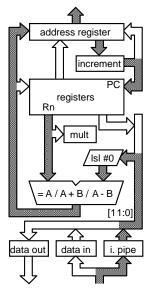

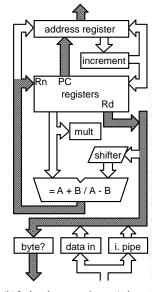

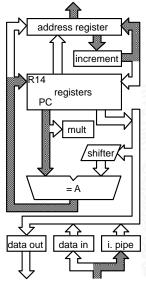

- Registerbank (inkl. Program Counter)

- ► Inkrementer

- Adress-Register

- ALU, Multiplizierer, Shifter

- ► Speicherinterface (Data-In / -Out)

- Steuerwerk

- bis ARM 7: 3-stufige Pipeline fetch, decode, execute

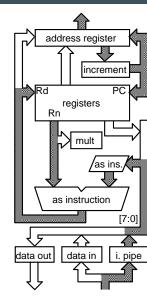

# ARM Datentransfer: Register-Operationen

Rechnerarchitektur - Wie arbeitet ein Rechners

Rd

Rn

address register

registers

mult

as instruction

data in

lincrement

Rm

as ins.

i. pipe

PC.

(b) register - immediate operations

[Fur00]

Rechnerarchitektur

data out

## ARM Datentransfer: Store-Befehl

Rechnerarchitektur - Wie arbeitet ein Rechner

Rechnerarchitektur

(a) 1st cycle - compute address

(b) 2nd cycle – store & auto-index

[Fur00]

# ARM Datentransfer: Funktionsaufruf/Sprungbefehl

Rechnerarchitektur - Wie arbeitet ein Rechner

Rechnerarchitektur

(a) 1st cycle - compute branch target

(b) 2nd cycle - save return address

[Fur00]

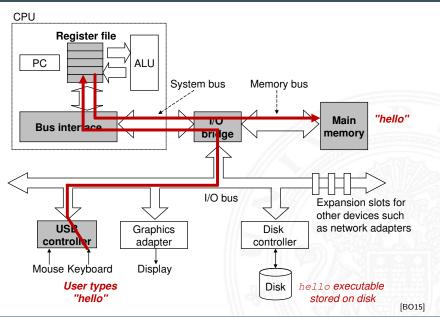

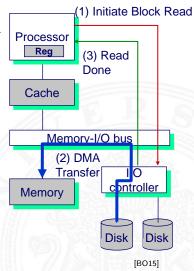

# Hardwareorganisation eines typischen Systems

Rechnerarchitektur - Wie arbeitet ein Rechner

## Programmausführung: 1. Benutzereingabe

Rechnerarchitektur - Wie arbeitet ein Rechner

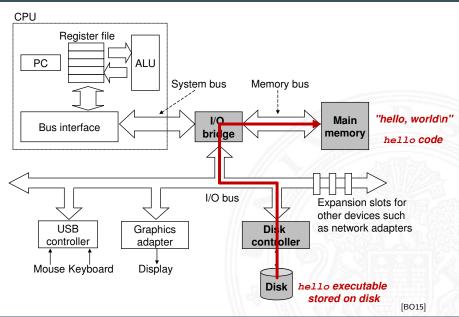

## Programmausführung: 2. Programm laden

Rechnerarchitektur - Wie arbeitet ein Rechner

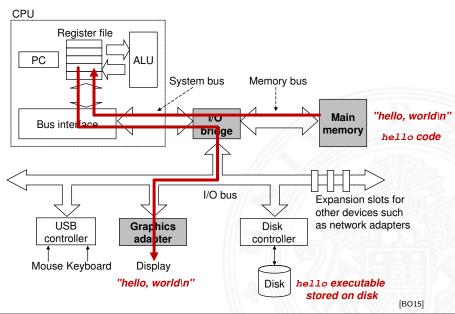

# Programmausführung: 3. Programmlauf

Rechnerarchitektur - Wie arbeitet ein Rechner

Bewertung von Architekturen und Rechnersystemen

- 1. Rechnerarchitektur

- 2. Bewertung von Architekturen und Rechnersystemen

Entwurfskriterien

Architekturbewertung

Kenngrößen

Amdahl's Gesetz

- 3. Instruction Set Architecture

- 4. Pipelining

- 5. Speicherhierarchie

- Architekt sucht beste Lösung im Suchraum möglicher Entwürfe

- Kriterien "guter" Architekturen:

- ▶ hohe Rechenleistung

- zuverlässig, robust

- modular, skalierbar

- einfach handhabbar, programmierbar

- orthogonal

- ausgewogen

- wirtschaftlich, adäquat

- . . . .

Begriffe, gelten für die *Mikroarchitektur* (Hardwarekomponenten) und den *Befehlssatz* (ISA)

- Skalierbarkeit Zusätzliche Hardware/Befehle verbessert das System

- $\Rightarrow$  Erweiterbarkeit, Performanz, Wirtschaftlichkeit

- Orthogonalität Jedes Modul/jeder Befehl hat eine definierte Funktionalität; keine zwei gleichartigen Module/Befehle

- ⇒ Wartbarkeit, Kosten, Handhabbarkeit

- Adäquatheit Kosten eines Moduls/Befehls entsprechen dessen Nutzen bzw. Funktionalität

- $\Rightarrow$  Kosten, Performanz

- Virtualität und Transparenz Virtuelle Hardware/ISA eliminiert physikalische Grenzen, (unwichtige) Details werden verborgen

- ⇒ skalierbar, Zuverlässigkeit, einfache Programmierung

- Fehlertransparenz System verbirgt, maskiert oder toleriert Fehler ⇒ Zuverlässigkeit

## Kenngrößen zur Bewertung

- Taktfrequenz

- ▶ Werte die sich aus Eigenschaften der Architektur ergeben

- Ausführungszeiten von Programmen

- Durchsätze

- ▶ statistische Größen

- **.** . . .

Die Wahl der Kenngrößen hängt entscheidend von der jeweiligen Zielsetzung ab

Bewertung von Architekturen und Rechnersystemen - Architekturbewertun

Rechnerarchitektur

### Verfahren zur Bestimmung der Kenngrößen

- Benchmarking: Laufzeitmessung bestehender Programme

- Standard Benchmarks

- SPEC Standard Performance Evaluation Corporation http://www.spec.org

- TPC Transaction Processing Performance Council http://www.tpc.org

- profilspezifische Benchmarks: SysMark, PCmark, Winbench etc.

- benutzereigene Anwendungsszenarien

- ► Monitoring: Messungen während des Betriebs

- ► Theoretische Verfahren: analytische Modelle, Simulation ...

### Taktfrequenz

- ► Seit Jahren Jahren erfolgreich beworben . . .

- ⇒ für die Leistungsbewertung aber völlig ungeeignet

#### theoretische Werte

- ► MIPS Million Instructions Per Second

- ► MFLOPS Million Floating Point Operations Per Second

- keine Angabe über die Art der Instruktionen und deren Ausführungszeit

- nicht direkt vergleichbar

- ▶ innerhalb einer Prozessorfamilie sinnvoll

Bewertung von Architekturen und Rechnersystemen - Kenngrößen

### Ausführungszeit

- ▶ Benutzer: Wie lange braucht mein Programm?

- Gesamtzeit: Rechenzeit + Ein-/Ausgabe, Platten- und Speicherzugriffe . . .

- ▶ CPU-Zeit: Unterteilung in System- und Benutzer-Zeit

```

Unix time-Befehl: 597.07u 0.15s 9:57.61 99.9%

```

597.07 user CPU time [sec.]

**0.15** system CPU time

9:57.61 elapsed time

99.9 CPU/elapsed [%]

## Theoretische Berechnung der CPU-Zeit (user CPU time)

- ightharpoonup CPU-Zeit =  $IC \cdot CPI \cdot T$

- IC Anzahl auszuführender InstruktionenCPI mittlere Anzahl Takte pro InstruktionCycles per Instruction

- T Taktperiode

- + IC kleiner: weniger Instruktionen

- bessere Algorithmen

- bessere Compiler

- mächtigere Befehle (CISC)

- + CPI kleiner: weniger Takte pro Instruktion

- einfachere Befehle (RISC)

- parallel Befehle ausführen: VLIW . . .

- parallel Teile der Befehle bearbeiten: Pipelining, superskalare Architekturen . . .

- + T kleiner: höhere Taktfrequenz

- bessere Technologie

- genauer, wenn CPI über die Häufigkeiten und Zyklenanzahl einzelner Befehle berechnet wird

- so lassen sich beispielsweise alternative Befehlssätze miteinander vergleichen

#### CPU-Durchsatz

- RZ-Betreiber

- Wie viele Aufträge kann die Maschine gleichzeitig verarbeiten?

- Wie lange braucht ein Job im Mittel?

- Wie viel Arbeit kann so pro Tag erledigt werden?

- ⇒ Latenzzeit: Wie lange dauert es, bis mein Job bearbeitet wird?

- ⇒ Antwortzeit: Wie lange rechnet mein Job?

- ► Modellierung durch Warteschlangentheorie: Markov-Ketten, stochastische Petri-Netze

## statistische Werte zur Zuverlässigkeit

- Betriebssicherheit des Systems: "Quality of Service"

- ► Fehlerrate: Fehlerursachen pro Zeiteinheit Ausfallrate: Ausfälle pro Zeiteinheit

- ► Fault: Fehlerursache

- ► Error: fehlerhafter Zustand

- ► Failure: ein Ausfall ist aufgetreten

- MTTF Mean Time To Failure

MTBF Mean Time Between Failures

MTTR Mean Time To Repair

MTBR Mean Time Between Repairs

...

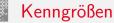

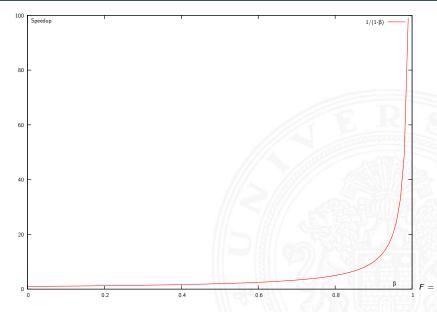

# Speedup

Wie wirken sich Verbesserungen der Rechnerarchitektur aus?

▶ Speedup: Verhältnis von Ausführungszeiten *T vor* und *nach* der Verbesserung

$$\mathsf{Speedup} = \mathit{T}_{\mathsf{vor}\mathit{Verbesserung}} / \mathit{T}_{\mathsf{nach}\mathit{Verbesserung}}$$

▶ Teile der Berechnung (0  $\leq \beta \leq 1$ ) werden um Faktor *F* beschleunigt:  $T = T_{ohneFffekt} + T_{mitFffekt}$

$$T_n = T_{v,o} + T_{v,m}/F_{Verbesserung}$$

- $\Rightarrow$  möglichst großer Anteil  $\beta$

- ⇒ den "Normalfall", den häufigsten Fall beschleunigen, um den größten Speedup zu erreichen

- ► Gene Amdahl, Architekt der IBM S/360, 1967

- ursprüngliche Idee

- ▶ Parallelrechner mit n-Prozessoren (= F)

- ▶ Parallelisierung der Aufgabe, bzw. einer Teilaufgabe

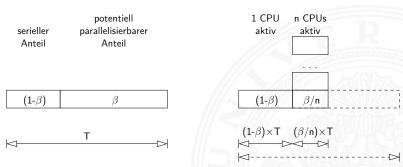

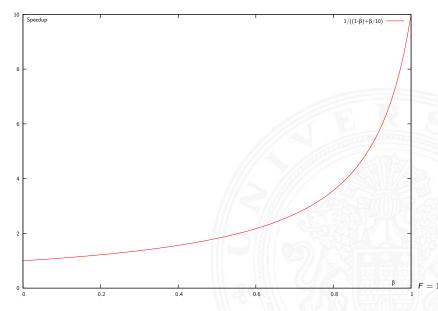

#### Amdahl's Gesetz

Speedup

$$= rac{1}{(1-eta)+f_k(n)+eta/n} \leq rac{1}{(1-eta)}$$

, mit  $eta = [0,1]$

# Prozessoren als Verbesserungsfaktor

Anteil parallelisierbarer Berechnung

$1-\beta$  Anteil nicht parallelisierbarer Berechnung

$f_k()$ Kommunikationsoverhead zwischen den Prozessoren

- Aufgaben verteilen

- Arbeit koordinieren

- Ergebnisse zusammensammeln

A. Mädei

# Amdahl's Gesetz: Beispiele

Bewertung von Architekturen und Rechnersystemen - Amdahl's Gesetz

Rechnerarchitektur

| n     | $\beta$ | Speedup                      |

|-------|---------|------------------------------|

| 10    | 0, 1    | 1/(0,9 +0,01) = 1,1          |

| 2     | 0,5     | 1/(0,5 +0,25) = 1,33         |

| 2     | 0,9     | 1/(0,1 +0,45) = 1,82         |

| 1, 1  | 0,98    | 1/(0,02+0,89) = 1,1          |

| 4     | 0,5     | 1/(0,5 +0,125) = 1,6         |

| 4 536 | 0,8     | 1/(0,2 +0,0) = 5,0           |

| 9 072 | 0,99    | $1/(0,01+0,0\ldots) = 98,92$ |

|       |         |                              |

- Optimierung bringt nichts, wenn der nicht beschleunigte ",serielle" Anteil  $(1 - \beta)$  eines Programms überwiegt

- ▶ *n*-Prozessoren (große *F*) wirken *nicht linear*

- ▶ Parallelität in Hochsprachen-Programmen ist meist gering, typischerweise: Speedup < 4 Multitasking und mehrere Prozesse: große  $\beta$

# Amdahl's Gesetz: Beispiele (cont.)

Bewertung von Architekturen und Rechnersystemen - Amdahl's Gesetz

# Amdahl's Gesetz: Beispiele (cont.)

Bewertung von Architekturen und Rechnersystemen - Amdahl's Gesetz

Rechnerarchitektur

# Amdahl's Gesetz: Beispiele (cont.)

Bewertung von Architekturen und Rechnersystemen - Amdahl's Gesetz

Rechnerarchitektur

Instruction Set Architecture

- 1. Rechnerarchitektur

- 2. Bewertung von Architekturen und Rechnersystemen

- 3. Instruction Set Architecture

Speicherorganisation

Befehlssatz

Befehlsformate

Adressierungsarten

Befehlssätze

- 4. Pipelining

- 5. Speicherhierarchie

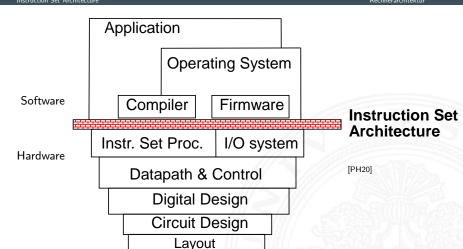

Instruction Set Architecture

Rechnerarchitektur

Instruction Set Architecture Rechnerarchitektur

### ISA - Instruction Set Architecture

- ⇒ alle für den Programmierer sichtbaren Attribute eines Rechners

- der (konzeptionellen) Struktur

- Funktionseinheiten der Hardware:

Recheneinheiten, Speicher, Verbindungssysteme

- des Verhaltens

- Organisation des programmierbaren Speichers

- ▶ Datentypen und Datenstrukturen: Codierungen und Darstellungen

- Befehlssatz

- Befehlsformate

- ► Modelle für Befehls- und Datenzugriffe

- Ausnahmebedingungen

Rechnerarchitektur

Instruction Set Architecture

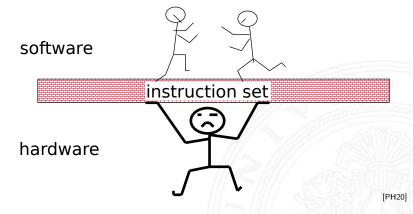

▶ Befehlssatz: die zentrale Schnittstelle

## Merkmale der Instruction Set Architecture

Instruction Set Architecture

Rechnerarchitektur

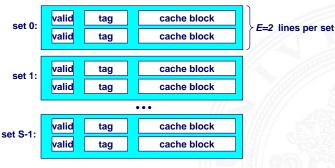

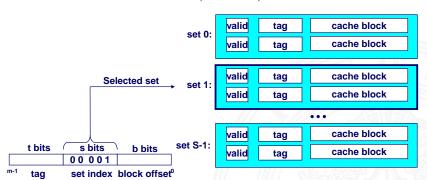

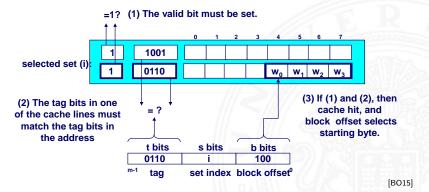

► Speichermodell Wortbreite, Adressierung . . .

► Rechnerklasse Stack-/Akku-/Registermaschine

► Registersatz Anzahl und Art der Rechenregister

► Befehlssatz Definition aller Befehle

► Art, Zahl der Operanden Anzahl/Wortbreite/Reg./Speicher

► Ausrichtung der Daten Alignment/Endianness

► Ein- und Ausgabe, Unterbrechungsstruktur (Interrupts)

Systemsoftware Loader, Assembler, Compiler, Debugger

Rechnerarchitektur

Instruction Set Architecture - Speicherorganisation

- Datentypen: Abspeichern von Zahlen, Zeichen, Strings?

- kleinster Datentyp üblicherweise ein Byte (8-bit)

- ▶ andere Daten als Vielfache: 16-bit, 32-bit, 64-bit . . .

- Organisation und Adressierung des Speichers?

- ► Adressen typisch in Bytes angegeben (x86-Architektur)

- erlaubt Adressierung einzelner ASCII-Zeichen usw.

- ▶ aber Maschine/Prozessor arbeitet wortweise

# Speicherorganisation (cont.)

Instruction Set Architecture - Speicherorganisatio

Rechnerarchitektur

- Speicher Wort-orientiert

- Adressierung Byte-orientiert

- die Adresse des ersten Bytes im Wort

- Adressen aufeinanderfolgender Worte unterscheiden sich um 4 (32-bit Wort) oder 8 (64-bit)

- Adressen normalerweise Vielfache der Wortlänge

- verschobene Adressen "in der Mitte" eines Worts oft unzulässig

|    | 32-bit<br>Nords | 64-b<br>Word | Bytes    | Addr. |

|----|-----------------|--------------|----------|-------|

|    | Addr            |              |          | 0000  |

|    | =               |              |          | 0001  |

|    | 0000            |              |          | 0002  |

|    |                 | Addı         | ´        | 0003  |

|    | Addr = 0004     | 0000         | )        | 0004  |

| g  |                 |              |          | 0005  |

| 9  |                 |              |          | 0006  |

| 4  |                 |              |          | 0007  |

|    |                 |              |          | 0008  |

| 6  | Addr<br>=       |              |          | 0009  |

| // | 0008            | Addı         | .        | 0010  |

| 9  |                 |              |          | 0011  |

| 1  |                 | 0008         | <u> </u> | 0012  |

|    | Addr<br>=       |              |          | 0013  |

|    | 0012            |              |          | 0014  |

| м  |                 |              |          | 0015  |

A. Mäder 45

[BO15]

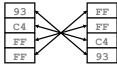

# Byte-Order

- Wie sollen die Bytes innerhalb eines Wortes angeordnet werden?

- ► Speicher wort-basiert ⇔ Adressierung byte-basiert

## Zwei Möglichkeiten / Konventionen:

- ▶ Big Endian: Sun, Mac usw. das MSB (most significant byte) hat die kleinste Adresse das LSB (least significant byte) hat die höchste -"-

- ► Little Endian: Alpha, x86 das MSB hat die höchste, das LSB die kleinste Adresse

satirische Referenz auf Gulliver's Reisen (Jonathan Swift)

## Big- vs. Little Endian

Instruction Set Architecture - Speicherorganisation

Rechnerarchitektur

| Adresse |    | Big E   | ndian    |              |    | Little E | Endian   |      | Adresse |        |

|---------|----|---------|----------|--------------|----|----------|----------|------|---------|--------|

| 0       | 0  | 1       | 2        | 3            | 3  | 2        | 1        | 0    | О       |        |

| 4       | 4  | 5       | 6        | 7            | 7  | 6        | 5        | 4    | 4       |        |

| 8       | 8  | 9       | 10       | 11           | 11 | 10       | 9        | 8    | 8       |        |

| 12      | 12 | 13      | 14       | 15           | 15 | 14       | 13       | 12   | 12      |        |

| ·       |    | 00 D    |          | Byte         |    | 00 D:    |          | Byte |         | D      |

|         | •  | – 32-Bi | t-Wort - | <del>_</del> | 4  | - 32-Bit | t-Wort - |      |         | [TA14] |

- ► Anordnung einzelner Bytes in einem Wort (hier 32 bit)

- Big Endian (n ... n + 3): MSB...LSB "String"-Reihenfolge

- Little Endian  $(n \dots n + 3)$ : LSB ... MSB "Zahlen"-Reihenfolge

- beide Varianten haben Vor- und Nachteile

- ggf. Umrechnung zwischen beiden Systemen notwendig

int A = 15213;int B = -15213;long int C = 15213; Dezimal: 15213

Binär: 0011 1011 0110 1101

Hex: в 6 D

#### Linux/Alpha A Sun A 6D 00 3B 00 00

#### Linux/Alpha B Sun B

[BO15]

Instruction Set Architecture - Speicherorganisation

Rechnerarchitektur

```

/* JimSmith.c - example record for byte-order demo */

typedef struct employee {

int

age;

int salary;

char name[12];

} employee_t;

static employee_t jimmy = {

// 0x0017

23,

// 0xc350

50000,

"Jim Smith", //J=0x4a \ i=0x69 \ usw.

};

```

```

tams12> objdump -s JimSmith.x86.o

JimSmith.x86.o: file format elf32-i386

Contents of section .data:

0000 17000000 50c30000 4a696d20 536d6974 ....P....Jim Smit

0010 68000000

h . . .

tams12 > objdump -s JimSmith.sparc.o

JimSmith.sparc.o: file format elf32-sparc

Contents of section .data:

0000 00000017 0000c350 4a696d20 536d6974 ......PJim Smit

0010 68000000

h . . .

```

Instruction Set Architecture - Speicherorganisation Rechnerarchitektur

[TA14]

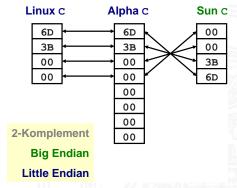

- Beispiel: 8-Byte-Wort in Little Endian Speicher

- "aligned" bezüglich Speicherwort

- "non aligned" an Byte-Adresse 12

- ► Speicher wird (meistens) Byte-weise adressiert aber Zugriffe lesen/schreiben jeweils ein ganzes Wort

- ⇒ was passiert bei "krummen" (misaligned) Adressen?

- automatische Umsetzung auf mehrere Zugriffe

Programmabbruch

(x86)

(SPARC)

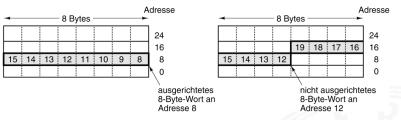

- ► CPU kann im Prinzip alle möglichen Adressen ansprechen

- ▶ in der Regel: kein voll ausgebauter Speicher 32 bit Adresse entsprechen 4 GiB Hauptspeicher, 64 bit . . .

- ► Aufteilung in RAM und ROM-Bereiche

- ▶ ROM mindestens zum Booten notwendig

- ► zusätzliche Speicherbereiche für "memory mapped" I/O

- ⇒ "Memory Map"

- Adressdecoder

- Hardwareeinheit

- ► Zuordnung von Adressen zu "realem" Speicher

32-bit ARM Proz.  $4 \times 8$ -bit SRAMs  $4 \times 8$ -bit ROMs

[Fur00]

#### Instruction Set Architecture - Speicherorganisation

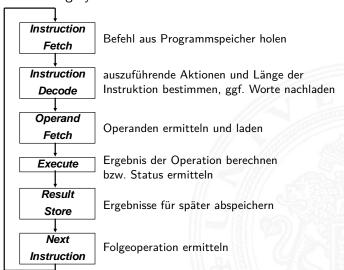

- Befehlszyklus

- ► Befehlsklassen

- Registermodell

- ► n-Adress Maschine

- Adressierungsarten

Instruction Set Architecture - Befehlssatz

- ► Prämisse: von-Neumann Prinzip

- ▶ Daten und Befehle im gemeinsamen Hauptspeicher

- ▶ Abarbeitung des Befehlszyklus in Endlosschleife

- Programmzähler PC adressiert den Speicher

- gelesener Wert kommt in das Befehlsregister IR

- Befehl decodieren

- Befehl ausführen

- nächsten Befehl auswählen

- benötigte Register

#### Steuerwerk

| PC         | Program Counter      | Adresse des Befehls        |

|------------|----------------------|----------------------------|

| IR         | Instruction Register | aktueller Befehl           |

| Rechenwerk |                      |                            |

| R0R31      | Registerbank         | Rechenregister (Operanden) |

| ACC        | Akkumulator          | = Minimalanforderung       |

Instruction Set Architecture - Befehlssatz

Rechnerarchitektur

- 1. Programmzähler (PC) liefert Adresse für den Speicher

- 2. Lesezugriff auf den Speicher

- 3. Resultat wird im Befehlsregister (IR) abgelegt

- 4. Programmzähler wird inkrementiert (ggf. auch später)

- ▶ Beispiel für 32 bit RISC mit 32 bit Befehlen

- ▶ IR = MEM[PC]

- ▶ PC = PC + 4

- bei CISC-Maschinen evtl. weitere Zugriffe notwendig, abhängig von der Art (und Länge) des Befehls

## Instruction Decode "Befehl decodieren" Phase im Befehlszyklus

Instruction Set Architecture - Befehlssatz

Rechnerarchitektur

- Befehl steht im Befehlsregister IR

- 1. Decoder entschlüsselt Opcode und Operanden

- 2. leitet Steuersignale an die Funktionseinheiten

## Operand Fetch

wird meist zu anderen Phasen hinzugezählt RISC: Teil von Instruction Decode CISC: -"- Instruction Execute

1. Operanden holen

## Instruction Execute "Befehl ausführen" Phase im Befehlszyklus

Instruction Set Architecture - Befehlssatz

Rechnerarchitektur

- Befehl steht im Befehlsregister IR

- Decoder hat Opcode und Operanden entschlüsselt

- Steuersignale liegen an Funktionseinheiten

- Ausführung des Befehls durch Aktivierung der Funktionseinheiten

- 2. ggf. Programmzähler setzen/inkrementieren

- Details abhängig von der Art des Befehls

- Ausführungszeit

- Realisierung

- fest verdrahtete Hardware

- mikroprogrammiert

A. Mädei

Instruction Set Architecture - Befehlssatz

Rechnerarchitektur

| Befehlsklassen                          | Beispiele                         |

|-----------------------------------------|-----------------------------------|

| ► arithmetische Operationen             | add, sub, inc, dec, mult, div     |

| logische Operationen                    | and, or, xor                      |

| schiebe Operationen                     | shl, sra, srl, ror                |

| <ul><li>Vergleichsoperationen</li></ul> | cmpeq, cmpgt, cmplt               |

| <ul><li>Datentransfers</li></ul>        | load, store, I/O                  |

| ► Programm-Kontrollfluss                | jump, jmpeq, branch, call, return |

| <ul><li>Maschinensteuerung</li></ul>    | trap, halt, (interrupt)           |

|                                         |                                   |

⇒ Befehlssätze und Computerarchitekturen

(Details später)

CISC – Complex Instruction Set Computer RISC – Reduced Instruction Set Computer

Instruction Set Architecture - Befehlssatz

- ▶ Befehlsregister IR enthält den aktuellen Befehl

- ▷ z.B. einen 32-bit Wert

Wie soll die Hardware diesen Wert interpretieren?

- direkt in einer Tabelle nachschauen (Mikrocode-ROM)

- ▶ Problem: Tabelle müsste 2<sup>32</sup> Einträge haben

- ⇒ Aufteilung in Felder: Opcode und Operanden

- ⇒ Decodierung über mehrere, kleine Tabellen

- ⇒ unterschiedliche Aufteilung für unterschiedliche Befehle: Befehlsformate

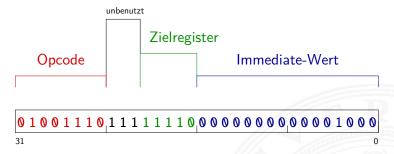

Instruction Set Architecture - Befehlsformate

Befehlsformat: Aufteilung in mehrere Felder

Opcode eigentlicher Befehl

ALU-Operation add/sub/incr/shift/usw.

► Register-Indizes Operanden / Resultat

► Speicher-Adressen für Speicherzugriffe

► Immediate-Operanden Werte direkt im Befehl

► Lage und Anzahl der Felder abhängig vom Befehlssatz

- festes Befehlsformat

- ▶ alle Befehle sind 32 Bit lang

- Opcode-Feld ist immer 6-bit breit

- codiert auch verschiedene Adressierungsmodi

nur 3 Befehlsformate: R, I, J

- R-Format

- ► Register-Register ALU-Operationen

- ► I-/J-Format

- ► Lade- und Speicheroperationen

- alle Operationen mit unmittelbaren Operanden

- Jump-Register

- ► Jump-and-Link-Register

Instruction Set Architecture - Befehlsformate

Rechnerarchitektur

- entwickelt an der Univ. Stanford, seit 1982

- ► Einsatz: eingebettete Systeme, SGI Workstations/Server

- klassische 32-bit RISC Architektur

- ▶ 32-bit Wortbreite, 32-bit Speicher, 32-bit Befehle

- ▶ 32 Register: R0 ist konstant Null, R1...R31 Universalregister

- ► Load-Store Architektur, nur base+offset Adressierung

- sehr einfacher Befehlssatz, 3-Adress-Befehle

- ▶ keinerlei HW-Unterstützung für "komplexe" SW-Konstrukte

- ► SW muss sogar HW-Konflikte ("Hazards") vermeiden

- ► Koprozessor-Konzept zur Erweiterung

Rechnerarchitektur

Instruction Set Architecture - Befehlsformate

- ▶ 32 Register, R0...R31, jeweils 32-bit

- ▶ R1 bis R31 sind Universalregister

- ▶ R0 ist konstant Null (ignoriert Schreiboperationen)

R0 Tricks

$$R5 = -R5$$

sub  $R5$ ,  $R0$ ,  $R5$   $R4 = 0$  add  $R4$ ,  $R0$ ,  $R0$   $R3 = 17$  addi  $R3$ ,  $R0$ ,  $R0$  if  $(R2 == 0)$  bne  $R2$ ,  $R0$ ,  $R0$

- keine separaten Statusflags

- ▶ Vergleichsoperationen setzen Zielregister auf 0 bzw. 1

$$R1 = (R2 < R3)$$

slt R1, R2, R3

- Übersicht und Details: [PH20, PH16]

David A. Patterson, John L. Hennessy: Rechnerorganisation und Rechnerentwurf – Die Hardware/Software-Schnittstelle

- dort auch hervorragende Erläuterung der Hardwarestruktur

- klassische fünf-stufige Befehlspipeline

Instruction-Fetch

Decode

Execute

Memory

Write-Back

Befehl holen

Decodieren und Operanden holen

ALU-Operation oder Adressberechnung

Speicher lesen oder schreiben

Resultat in Register speichern

Rechnerarchitektur

Instruction Set Architecture - Befehlsformate

PC I-Cache Register (R0 .. R31)

ALUs

Speicher D-Cache

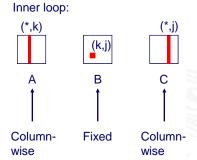

# MIPS: Befehlsformate Befehl im R-Format

Instruction Set Architecture - Befehlsformate

Rechnerarchitektur

| 000000 | 10,111 | 11110  | 00011  | 0 0 0 0 0 | 100010 |

|--------|--------|--------|--------|-----------|--------|

| 31     |        |        |        |           | 0      |

| 6 bits | 5 bits | 5 bits | 5 bits | 5 bits    | 6 bits |

| ор     | rs     | rt     | rd     | shift     | funct  |

| <b>•</b> | op:    | Opcode               | Typ des Befehls      | <b>0</b> = ,,alu-op <sup>6</sup> |

|----------|--------|----------------------|----------------------|----------------------------------|

|          | rs:    | source register 1    | erster Operand       | 23 = "r23"                       |

|          | rt:    | source register 2    | zweiter Operand      | 30 = "r30"                       |

|          | rd:    | destination register | Zielregister         | 3 = ,,r3"                        |

|          | shift: | shift amount         | (optionales Shiften) | <b>0</b> = ,,0"                  |

|          | funct: | ALU function         | Rechenoperation      | 34 = "sub"                       |

$\Rightarrow$  r3 = r23 - r30 sub r3, r23, r30

# MIPS: Befehlsformate Befehl im I-Format

Instruction Set Architecture - Befehlsformate

Rechnerarchitektur

| 100011 | 0 1 0 0 0 | 00101  | 000000000000000110 |

|--------|-----------|--------|--------------------|

| 31     |           |        | (                  |

| 6 bits | 5 bits    | 5 bits | 16 bits            |

| ор     | rs        | rt     | address            |

▶ op: Opcode Typ des Befehls 35 = "lw"

rs: base register Basisadresse 8 = "r8"

rt: destination register Zielregister 5 = "r5"

addr: address offset Offset 6 = "6"

$$\Rightarrow r5 = MEM[r8+6]$$

lw r5, 6(r8)

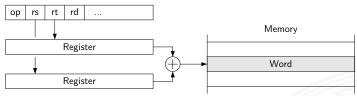

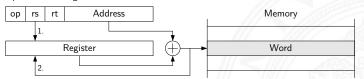

- ▶ Woher kommen die Operanden / Daten für die Befehle?

- Hauptspeicher, Universalregister, Spezialregister

- ▶ Wie viele Operanden pro Befehl?

- ▶ 0- / 1- / 2- / 3-Adress Maschinen

- ► Wie werden die Operanden adressiert?

- ▶ immediate / direkt / indirekt / indiziert / autoinkrement / usw.

- ⇒ wichtige Unterscheidungsmerkmale für Rechnerarchitekturen

- lacktriangle Zugriff auf Hauptspeicher: pprox 100 imes langsamer als Registerzugriff

- ▶ möglichst Register statt Hauptspeicher verwenden (!)

- "load/store"-Architekturen

- ▶ Rechner soll "rechnen" können

- typische arithmetische Operation nutzt 3 Variablen Resultat, zwei Operanden: X = Y + Z

add r2, r4, r5 reg2 = reg4 + reg5

"addiere den Inhalt von R4 und R5 und speichere das Resultat in R2"

- woher kommen die Operanden?

- wo soll das Resultat hin?

- Speicher

- Register

- entsprechende Klassifikation der Architektur

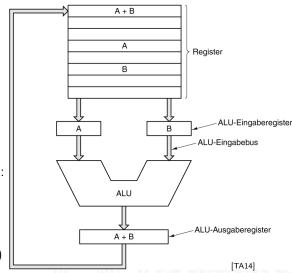

Rechnerarchitektur

Instruction Set Architecture - Adressierungsarten

- Register (-bank)

- ► liefern Operanden

- speichern Resultate

- ▶ interne Hilfsregister

- ► ALU, typ. Funktionen:

- ► add, add-carry, sub

- and, or, xor

- shift, rotate

- compare

- ▶ (floating point ops.)

Instruction Set Architecture - Adressierungsarter

Rechnerarchitektur

addr1

- typische Architektur

- von-Neumann Prinzip: alle Daten im Hauptspeicher

- ▶ 3-Adress-Befehle: zwei Operanden, ein Resultat

- data1

addr2

data2

addr3

data1

- ⇒ "Multiport-Speicher" mit drei Ports?

- sehr aufwändig, extrem teuer, trotzdem langsam

- ⇒ Register im Prozessor zur Zwischenspeicherung!

- Datentransfer zwischen Speicher und Registern

Load reg = MEM[addr]

Store MEM[addr] = reg

- Regs

- ▶ RISC: Rechenbefehle arbeiten *nur* mit Registern

- ► CISC: gemischt, Operanden in Registern oder im Speicher

3-Adress Format

- ► X = Y + Z

- sehr flexibel, leicht zu programmieren

- ▶ Befehl muss 3 Adressen codieren

2-Adress Format

- ▶ X = X + Z

- eine Adresse doppelt verwendet: für Resultat und einen Operanden

- Format wird häufig verwendet

1-Adress Format

- ightharpoonup ACC = ACC + Z

- alle Befehle nutzen das Akkumulator-Register

- ▶ häufig in älteren / 8-bit Rechnern

0-Adress Format

- ► TOS = TOS + NOS

- ▶ Stapelspeicher: top of stack, next of stack

- Adressverwaltung entfällt

▶ im Compilerbau beliebt

Instruction Set Architecture - Adressierungsarten

Rechnerarchitektur

Beispiel: Z = (A-B) / (C + D\*E)

Hilfsregister: T

#### 3-Adress Maschine

sub Z, A, B

mul T, D, E add T, C, T

div Z, Z, T

#### 2-Adress Maschine

mov Z, A

sub Z, B

mov T, D

mul T, E

add T, C

div Z, T

#### 1-Adress Maschine

load D

mul E

stor 2

load A

div Z

В

sub

stor Z

### 0-Adress Maschine

push E push D

mul

push C

add push B

push A

sub

div

pop Z

# Beispiel: Stack-Maschine / 0-Adress Maschine

Instruction Set Architecture - Adressierungsarten

Rechnerarchitektur

Beispiel: Z = (A-B) / (C + D\*E)

| 0-Adre | ess Maschin |

|--------|-------------|

| push   | E           |

| push   | D           |

| mul    |             |

| push   | С           |

| add    |             |

| push   | В           |

| push   | A           |

| sub    |             |

| div    |             |

| non    | 7           |

| TOS           | NOS   | <b></b> | Stack |

|---------------|-------|---------|-------|

| Е             |       |         |       |

| D             | Е     |         |       |

| D*E           |       |         |       |

| С             | D*E   |         |       |

| C+D*E         |       |         |       |

| В             | C+D*E |         |       |

| Α             | В     | C+D*E   |       |

| A-B           | C+D*E |         |       |

| (A-B)/(C+D*E) |       |         |       |

|               |       |         |       |

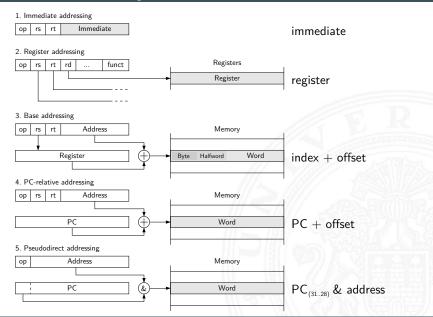

- "immediate"

- ► Operand steht direkt im Befehl

- kein zusätzlicher Speicherzugriff

- aber Länge des Operanden beschränkt

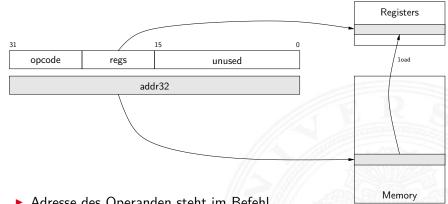

- "direkt"

- ► Adresse des Operanden steht im Befehl

- keine zusätzliche Adressberechnung

- ein zusätzlicher Speicherzugriff

- Adressbereich beschränkt

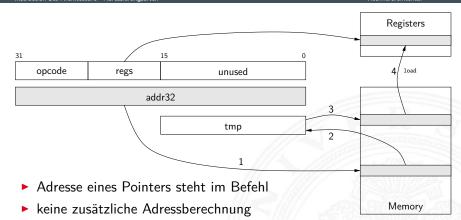

- "indirekt"

- Adresse eines Pointers steht im Befehl

- erster Speicherzugriff liest Wert des Pointers

- zweiter Speicherzugriff liefert Operanden

- sehr flexibel (aber langsam)

- "register"

- wie Direktmodus, aber Register statt Speicher

- 32 Register: benötigen 5 bit im Befehl

- genug Platz für 2- oder 3-Adress Formate

- "register-indirekt"

- ► Befehl spezifiziert ein Register

- mit der Speicheradresse des Operanden

- ein zusätzlicher Speicherzugriff

- "indiziert"

- Angabe mit Register und Offset

- ► Inhalt des Registers liefert Basisadresse

- Speicherzugriff auf (Basisadresse+offset)

- ▶ ideal für Array- und Objektzugriffe

- ► Hauptmodus in RISC-Rechnern (auch: "Versatz-Modus")

# Immediate Adressierung

Instruction Set Architecture - Adressierungsarten

Rechnerarchitektur

| opcode      | regs | immediate16 |

|-------------|------|-------------|

| 31          |      | 15 0        |

| opcode regs |      | unused      |

1-Wort Befehl

2-Wort Befehl

#### immediate32

- Operand steht direkt im Befehl, kein zusätzlicher Speicherzugriff

- ► Länge des Operanden < (Wortbreite Opcodebreite)

- ▶ Darstellung größerer Zahlenwerte

- ► 2-Wort Befehle zweites Wort für Immediate-Wert

(x86)

mehrere Befehle

z.B. obere/untere Hälfte eines Wortes

(MIPS, SPARC)

► Immediate-Werte mit zusätzlichem Shift

(ARM)

Instruction Set Architecture - Adressierungsarten

Rechnerarchitektur

- ► Adresse des Operanden steht im Befehl

- keine zusätzliche Adressberechnung

- ▶ ein zusätzlicher Speicherzugriff: z.B. R3 = MEM[addr32]

- ► Adressbereich beschränkt, oder 2-Wort Befehl (wie Immediate)

Instruction Set Architecture - Adressierungsarten

- zwei zusätzliche Speicherzugriffe:z.B. tmp = MEM[addr32] R3 = MEM[tmp]

- ▶ typische CISC-Adressierungsart, viele Taktzyklen

- kommt bei RISC-Rechnern nicht vor

Rechnerarchitektur

Instruction Set Architecture - Adressierungsarten

#### Updateaddressing

- ▶ indizierte Adressierung, z.B. für Arrayzugriffe

- ▶  $addr = \langle Sourceregister \rangle + \langle Basisregister \rangle$

- ▶ addr = ⟨Sourceregister⟩ + offset; Sourceregister = addr

# Beispiel: MIPS Adressierungsarten

Instruction Set Architecture - Adressierungsarten

Rechnerarchitektur

Instruction Set Architecture - Adressierungsarter

Rechnerarchitektur

## welche Adressierungsarten / -Varianten sind üblich?

▶ 0-Adress (Stack-) Maschine Java virtuelle Maschine

► 1-Adress (Akkumulator) Maschine 8-bit Mikrocontroller einige x86 Befehle

► 2-Adress Maschine 16-bit Rechner

einige x86 Befehle

► 3-Adress Maschine 32-bit RISC

► CISC Rechner unterstützen diverse Adressierungsarten

RISC meistens nur indiziert mit Offset

siehe en.wikipedia.org/wiki/Addressing\_mode

### Kriterien für einen guten Befehlssatz

- vollständig: alle notwendigen Instruktionen verfügbar

- orthogonal: keine zwei Instruktionen leisten das Gleiche

- ▶ symmetrisch: z.B. Addition ⇔ Subtraktion

- ▶ adäquat: technischer Aufwand entsprechend zum Nutzen

- effizient: kurze Ausführungszeiten

Rechnerarchitektur

Instruction Set Architecture - Befehlssätze

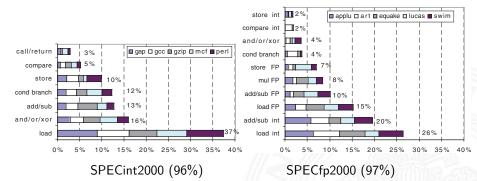

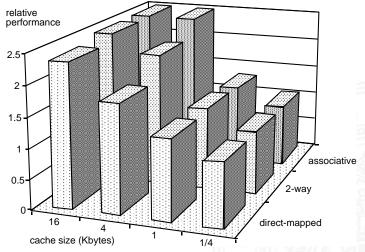

## Statistiken zeigen: Dominanz der einfachen Instruktionen

▶ x86-Prozessor

|      | Anweisung          | Ausführungshäufigkeit % |

|------|--------------------|-------------------------|

| 1.   | load               | 22 %                    |

| 2.   | conditional branch | 20 %                    |

| 3.   | compare            | 16 %                    |

| 4.   | store              | 12 %                    |

| 5.   | add                | 8 %                     |

| 6.   | and                | 6 %                     |

| 7.   | sub                | 5 %                     |

| 8.   | move reg-reg       | 4 %                     |

| 9.   | call               | 1 %                     |

| 10.  | return             | 1%                      |

| Tota | nl                 | 96 %                    |

# Bewertung der ISA (cont.)

Instruction Set Architecture - Befehlssätze

Rechnerarchitektur

| Instruction          | compress | eqntott | espresso | gcc (cc1) | li     | Int. average |

|----------------------|----------|---------|----------|-----------|--------|--------------|

| load                 | 20.8%    | 18.5%   | 21.9%    | 24.9%     | 23.3%  | 22%          |

| store                | 13.8%    | 3.2%    | 8.3%     | 16.6%     | 18.7%  | 12%          |

| add                  | 10.3%    | 8.8%    | 8.15%    | 7.6%      | 6.1%   | 8%           |

| sub                  | 7.0%     | 10.6%   | 3.5%     | 2.9%      | 3.6%   | 5%           |

| mul                  |          |         |          | 0.1%      |        | 0%           |

| div                  |          |         |          |           |        | 0%           |

| compare              | 8.2%     | 27.7%   | 15.3%    | 13.5%     | 7.7%   | 16%          |

| mov reg-reg          | 7.9%     | 0.6%    | 5.0%     | 4.2%      | 7.8%   | 4%           |

| load imm             | 0.5%     | 0.2%    | 0.6%     | 0.4%      | - 2    | 0%           |

| cond. branch         | 15.5%    | 28.6%   | 18.9%    | 17.4%     | 15.4%  | 20%          |

| uncond. branch       | 1.2%     | 0.2%    | 0.9%     | 2.2%      | 2.2%   | 1%           |

| call                 | 0.5%     | 0.4%    | 0.7%     | 1.5%      | 3.2%   | 1%           |

| return, jmp indirect | 0.5%     | 0.4%    | 0.7%     | 1.5%      | 3.2%   | 1%           |

| shift                | 3.8%     |         | 2.5%     | 1.7%      | 1      | 1%           |

| and                  | 8.4%     | 1.0%    | 8.7%     | 4.5%      | 8.4%   | 6%           |

| or                   | 0.6%     |         | 2.7%     | 0.4%      | 0.4%   | 1%           |

| other (xor, not,)    | 0.9%     |         | 2.2%     | 0.1%      | 1811-1 | 1%           |

| load FP              |          |         | - 1      | 11 15 1   | 10///  | 0%           |

| store FP             |          |         | - 1      | // 7/     | NY./   | 0%           |

| add FP               |          |         | - 11     | 1 10      | 777 (  | 0%           |

| sub FP               |          |         | - 11     | 1 N       | 11     | 0%           |

| mul FP               |          |         | 111      | LIIN      | 1 00/5 | 0%           |

| div FP               |          |         | - 171    | - 10      | I We   | 0%           |

| compare FP           |          |         |          | 13        |        | 0%           |

| mov reg-reg FP       |          |         | - 11     | 1.9       | 1 8    | 0%           |

| other (abs, sqrt,)   |          |         | 11       | 0.13      | 11 6   | 0%           |

[HP17]

Rechnerarchitektur

MIPS-Prozessor

[HP17]

- ► ca. 80 % der Berechnungen eines typischen Programms verwenden nur ca. 20 % der Instruktionen einer CPU

- ▶ am häufigsten gebrauchten Instruktionen sind einfache Instruktionen: load, store, add ...

- ⇒ Motivation f

ür RISC.

Rechnerarchitekturen mit irregulärem, komplexem Befehlssatz und (unterschiedlich) langer Ausführungszeit

- aus der Zeit der ersten Großrechner, 60er Jahre

- ▶ Programmierung auf Assemblerebene

- ► Komplexität durch sehr viele (mächtige) Befehle umgehen

### typische Merkmale

- ▶ Instruktionssätze mit mehreren hundert Befehlen (> 300)

- ▶ unterschiedlich lange Instruktionsformate: 1...n-Wort Befehle

- komplexe Befehlscodierung

- mehrere Schreib- und Lesezugriffe pro Befehl

- viele verschiedene Datentypen

- ▶ sehr viele Adressierungsarten, -Kombinationen

- ▶ fast alle Befehle können auf Speicher zugreifen

- Mischung von Register- und Speicheroperanden

- komplexe Adressberechnung

- ► Unterprogrammaufrufe: über Stack

- ▶ Übergabe von Argumenten

- ► Speichern des Programmzählers

- explizite "Push" und "Pop" Anweisungen

- Zustandscodes ("Flags")

- ▶ implizit gesetzt durch arithmetische und logische Anweisungen

### Vor- / Nachteile

- + nah an der Programmiersprache, einfacher Assembler

- + kompakter Code: weniger Befehle holen, kleiner I-Cache

- Befehlssatz vom Compiler schwer auszunutzen

- Ausführungszeit abhängig von: Befehl, Adressmodi ...

- Instruktion holen schwierig, da variables Instruktionsformat

- Speicherhierarchie schwer handhabbar: Adressmodi

- Pipelining schwierig

### Beispiele

► Intel x86 / IA-64, Motorola 68 000, DEC Vax

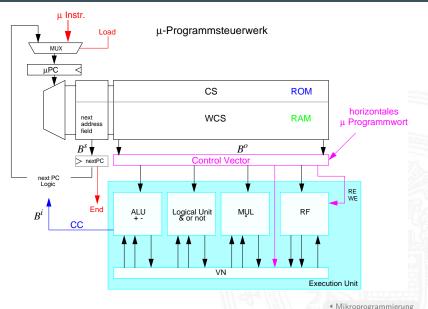

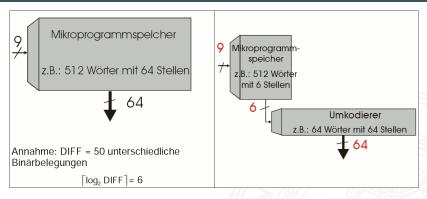

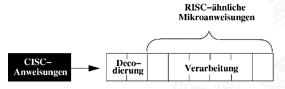

- ein Befehl kann nicht in einem Takt abgearbeitet werden

- ⇒ Unterteilung in Mikroinstruktionen (Ø 5 . . . 7)

- ► Ablaufsteuerung durch endlichen Automaten

- meist als ROM (RAM) implementiert, das Mikroprogrammworte beinhaltet

- 1. horizontale Mikroprogrammierung

- ► langes Mikroprogrammwort (ROM-Zeile)

- steuert direkt alle Operationen

- ► Spalten entsprechen: Kontrollleitungen und Folgeadressen

Instruction Set Architecture - Befehlssätze

Rechnerarchitektur

- kurze Mikroprogrammworte

- Spalten enthalten Mikrooperationscode

- mehrstufige Decodierung für Kontrollleitungen

- + CISC-Befehlssatz mit wenigen Mikrobefehlen realisieren

- + bei RAM: Mikrobefehlssatz austauschbar

- (mehrstufige) ROM/RAM Zugriffe: zeitaufwändig

# horizontale Mikroprogrammierung

Instruction Set Architecture - Befehlssätze

Rechnerarchitektur

## vertikale Mikroprogrammierung

Instruction Set Architecture - Befehlssätze

Rechnerarchitektur

◀ Mikroprogrammierung

### oft auch: "Regular Instruction Set Computer"

- Grundidee: Komplexitätsreduktion in der CPU

- seit den 80er Jahren: "RISC-Boom"

- ▶ internes Projekt bei IBM

- von Hennessy (Stanford) und Patterson (Berkeley) publiziert

- Hochsprachen und optimierende Compiler

- ⇒ kein Bedarf mehr für mächtige Assemblerbefehle

- ⇒ pro Assemblerbefehl muss nicht mehr "möglichst viel" lokal in der CPU gerechnet werden (CISC Mikroprogramm)

### Beispiele

► IBM 801, MIPS, SPARC, DEC Alpha, ARM

## typische Merkmale

- ▶ reduzierte Anzahl einfacher Instruktionen (z.B. 128)

- ▶ benötigen in der Regel mehr Anweisungen für eine Aufgabe

- werden aber mit kleiner, schneller Hardware ausgeführt

- ▶ reguläre Struktur, z.B. 32-bit Wortbreite, 32-bit Befehle

- nur ein-Wort Befehle

- lacktriangle alle Befehle in gleicher Zeit ausführbar  $\Rightarrow$  Pipeline-Verarbeitung

- ► Speicherzugriff *nur* durch "Load" und "Store" Anweisungen

- ▶ alle anderen Operationen arbeiten auf Registern

- keine Speicheroperanden

- ► Register-orientierter Befehlssatz

- ▶ viele universelle Register, keine Spezialregister (≥ 32)

- ▶ oft mehrere (logische) Registersätze: Zuordnung zu Unterprogrammen, Tasks etc.

- Unterprogrammaufrufe: über Register

- ► Register für Argumente, "Return"-Adressen, Zwischenergebnisse

- keine Zustandscodes ("Flags")

- spezielle Testanweisungen

- speichern Resultat direkt im Register

- optimierende Compiler statt Assemblerprogrammierung

# RISC - Reduced Instruction Set Computer (cont.)

Instruction Set Architecture - Befehlssätz

Rechnerarchitektu

### Vor- / Nachteile

- + fest-verdrahtete Logik, kein Mikroprogramm

- + einfache Instruktionen, wenige Adressierungsarten

- + Pipelining gut möglich

- + Cycles per Instruction = 1 in Verbindung mit Pipelining: je Takt (mind.) ein neuer Befehl

- längerer Maschinencode

- viele Register notwendig

- optimierende Compiler nötig / möglich

- ► High-performance Speicherhierarchie notwendig

## ursprüngliche Debatte

- streng geteilte Lager

- ▶ pro CISC: einfach für den Compiler; weniger Code Bytes

- pro RISC: besser für optimierende Compiler; schnelle Abarbeitung auf einfacher Hardware

#### aktueller Stand

- Grenzen verwischen

- ▶ RISC-Prozessoren werden komplexer

- ► CISC-Prozessoren weisen RISC-Konzepte oder gar RISC-Kern auf

- ▶ für Desktop Prozessoren ist die Wahl der ISA kein Thema

- ► Code-Kompatibilität ist sehr wichtig!

- ▶ mit genügend Hardware wird alles schnell ausgeführt

- eingebettete Prozessoren: eindeutige RISC-Orientierung

+ kleiner, billiger, weniger Leistungsverbrauch

- Restriktionen durch Hardware abgeschwächt

- Code-Kompatibilität leichter zu erfüllen

- ▶ Emulation in Firm- und Hardware

- ► Intel bewegt sich weg von IA-32

- erlaubt nicht genug Parallelität

hat IA-64 eingeführt ("Intel Architecture 64-bit")

- ⇒ neuer Befehlssatz mit expliziter Parallelität (EPIC)

- ⇒ 64-bit Wortgrößen (überwinden Adressraumlimits)

- ⇒ benötigt hoch entwickelte Compiler

Pipelining Rechnerarchitektur

- 1. Rechnerarchitektur

- 2. Bewertung von Architekturen und Rechnersystemen

- 3. Instruction Set Architecture

- 4. Pipelining

Motivation und Konzept

Befehlspipeline

**MIPS**

Bewertung

Hazards

Superskalare Rechner

5. Speicherhierarchie

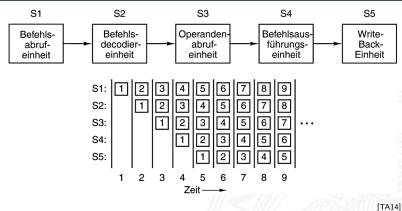

# Pipelining / Fließbandverarbeitung

Pipelining - Motivation und Konzep

Rechnerarchitektur

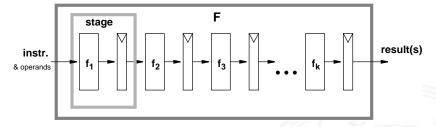

#### Grundidee

- ▶ Operation *F* kann in Teilschritte zerlegt werden

- ▶ jeder Teilschritt f; braucht ähnlich viel Zeit

- ightharpoonup Teilschritte  $f_1...f_k$  können parallel zueinander ausgeführt werden

- ► Trennung der Pipelinestufen ("stage") durch Register

- ightharpoonup Zeitbedarf für Teilschritt  $f_i \gg \text{Zugriffszeit}$  auf Register  $(t_{FF})$

Rechnerarchitektur

Pipelining - Motivation und Konzep

### Pipelining-Konzept

- Prozess in unabhängige Abschnitte aufteilen

- Objekt sequenziell durch diese Abschnitte laufen lassen

- zu jedem Zeitpunkt werden zahlreiche Objekte bearbeitet

- ▶ —"— sind alle Stationen ausgelastet

#### Konsequenz

- ▶ Pipelining lässt Vorgänge gleichzeitig ablaufen

- reale Beispiele: Autowaschanlagen, Fließbänder in Fabriken

### Arithmetische Pipelines

- ► Idee: lange Berechnung in Teilschritte zerlegen wichtig bei komplizierteren arithmetischen Operationen

- die sonst sehr lange dauern (weil ein großes Schaltnetz)

- ▶ die als Schaltnetz extrem viel Hardwareaufwand erfordern

- ▶ Beispiele: Multiplikation, Division, Fließkommaoperationen . . .

- + Erhöhung des Durchsatzes, wenn Berechnung mehrfach hintereinander ausgeführt wird

### Befehlspipeline im Prozessor

► Idee: die Phasen der von-Neumann Befehlsabarbeitung (Befehl holen, Befehl decodieren ...) als Pipeline implementieren

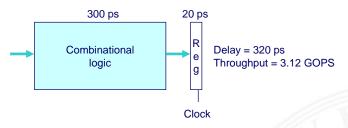

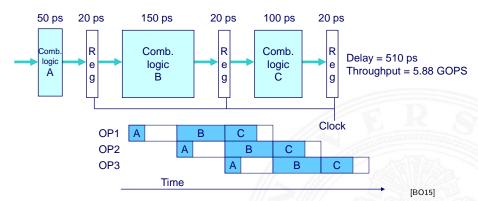

# Beispiel: Schaltnetz ohne Pipeline

Pipelining - Motivation und Konzept

Rechnerarchitektur

[BO15]

- ► Verarbeitung erfordert 300 ps

- weitere 20 ps um das Resultat im Register zu speichern

- ► Zykluszeit: mindestens 320 ps

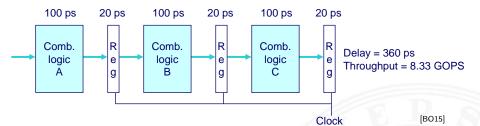

# Beispiel: Version mit 3-stufiger Pipeline

Pipelining - Motivation und Konzept

Rechnerarchitektur

- ► Kombinatorische Logik in 3 Blöcke zu je 100 ps aufgeteilt

- ▶ neue Operation, sobald vorheriger Abschnitt durchlaufen wurde

⇒ alle 120 ps neue Operation

- ▶ allgemeine Latenzzunahme

⇒ 360 ps von Start bis Ende

Dochnororchitoktur

[BO15]

Pipelining - Motivation und Konzept

▶ ohne Pipeline

▶ 3-stufige Pipeline

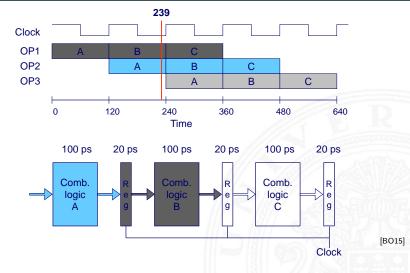

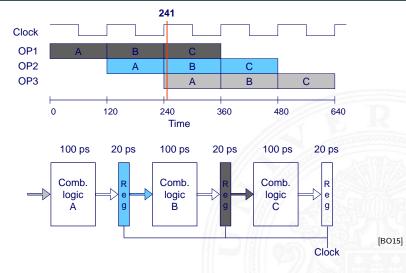

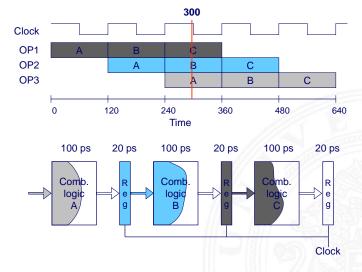

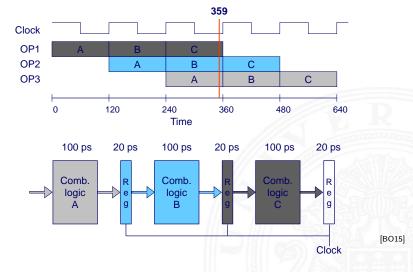

# Timing: 3-stufige Pipeline

Pipelining - Motivation und Konzept

Rechnerarchitektur

## Timing: 3-stufige Pipeline

Pipelining - Motivation und Konzept

Rechnerarchitektur

## Timing: 3-stufige Pipeline

Pipelining - Motivation und Konzept

Rechnerarchitektur

[BO15]

## Timing: 3-stufige Pipeline

Pipelining - Motivation und Konzept

Rechnerarchitektur

## Limitierungen: nicht uniforme Verzögerungen

Pipelining - Motivation und Konzept

Rechnerarchitektur

- ► Taktfrequenz limitiert durch langsamste Stufe

- ► Schaltung in möglichst gleich schnelle Stufen aufteilen

Pipelining - Motivation und Konzept

Rechnerarchitektur

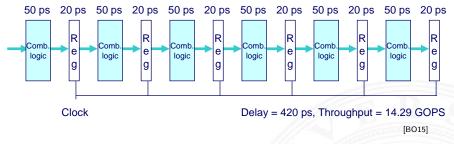

- registerbedingter Overhead wächst mit Pipelinelänge

- (anteilige) Taktzeit für das Laden der Register

Overhead Taktperiode

| 1-Register: | 6,25%  | 20 ps | 320 ps |

|-------------|--------|-------|--------|

| 3-Register: | 16,67% | 20 ps | 120 ps |

| 6-Register: | 28,57% | 20 ps | 70 ps  |

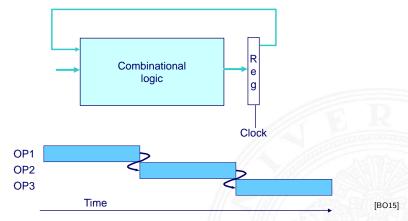

## Limitierungen: Datenabhängigkeiten

Pipelining - Motivation und Konzept

Rechnerarchitektur

▶ jede Operation hängt vom Ergebnis der Vorhergehenden ab

# Limitierungen: Datenabhängigkeiten (cont.)

Pipelining - Motivation und Konzept

Rechnerarchitektur

[BO15]

- ⇒ Resultat-Feedback kommt zu spät für die nächste Operation

- ⇒ Pipelining ändert Verhalten des gesamten Systems

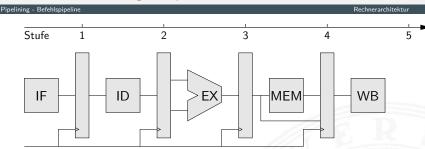

Pipelining - Befehlspipeline

Rechnerarchitektur

## typische Schritte der Befehlsabarbeitung (von ISA abhängig)

| ▶ IF | Instruction Fetch                           |

|------|---------------------------------------------|

|      | Instruktion holen, in Befehlsregister laden |

| ID   | Instruction Decode                          |

|      | Instruktion decodieren                      |

| OF   | Operand Fetch                               |

|      | Operanden aus Registern holen               |

| EX   | Execute                                     |

|      | ALU führt Befehl aus                        |

| MEM  | Memory access                               |

|      | Speicherzugriff: Daten laden/abspeichern    |

| WB   | Write Back                                  |

|      | Ergebnis in Register zurückschreiben        |

## von-Neumann Befehlszyklus (cont.)

Pipelining - Befehlspipeline

Rechnerarchitektur

- ▶ je nach Instruktion sind 3-5 dieser Schritte notwendig

- ▶ nop: nur Instruction-Fetch

- jump: kein Speicher-/Registerzugriff

- ► Schritte können auch feiner unterteilt werden (mehr Stufen)

## von-Neumann Befehlszyklus (cont.)

Pipelining - Befehlspipeline

Rechnerarchitektur

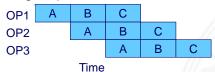

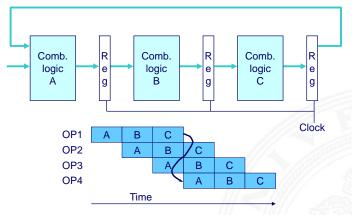

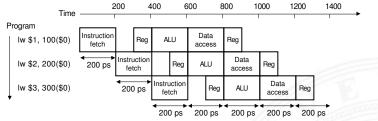

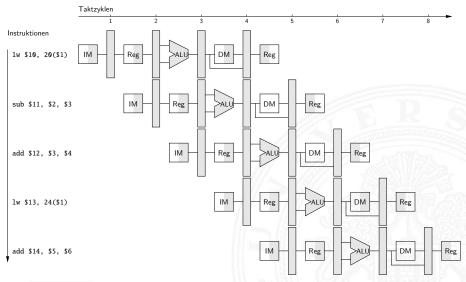

### Pipelining für die einzelnen Schritte der Befehlsausführung

[PH20]

- ▶ Befehle überlappend ausführen: neue Befehle holen, dann decodieren, während vorherige noch ausgeführt werden

- ► Register trennen Pipelinestufen

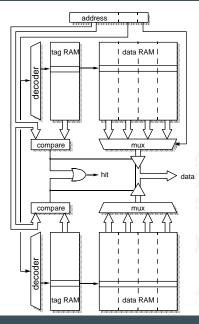

## Klassische 5-stufige Pipeline

- ► Grundidee der ursprünglichen RISC-Architekturen

- + Durchsatz ca.  $3...5 \times$  besser als serielle Ausführung

- + guter Kompromiss aus Leistung und Hardwareaufwand

► MIPS-Architektur (aus Patterson, Hennessy [PH16])

▶ MIPS ohne Pipeline

▶ MIPS Pipeline

▶ Pipeline Schema

Pipelining - Befehlspipeline Rechnerarchitektur

- ▶ RISC ISA: Pipelining wird direkt umgesetzt

- ▶ Befehlssätze auf diese Pipeline hin optimiert

- ► IBM-801, MIPS R-2000/R-3000 (1985), SPARC (1987)

- ► CISC-Architekturen heute ebenfalls mit Pipeline

- Motorola 68020 (zweistufige Pipeline, 1984),

Intel 486 (1989), Pentium (1993) . . .

- ▶ Befehle in Folgen RISC-ähnlicher Anweisungen umsetzen

- + CISC-Software bleibt lauffähig

- + Befehlssatz wird um neue RISC Befehle erweitert

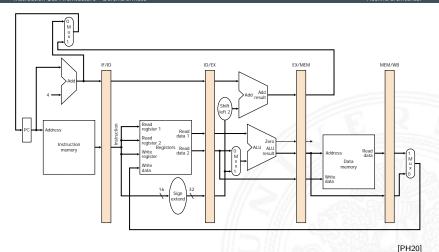

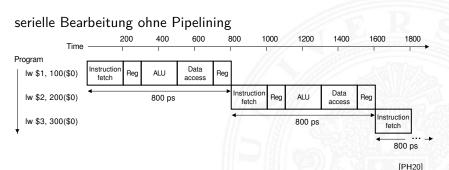

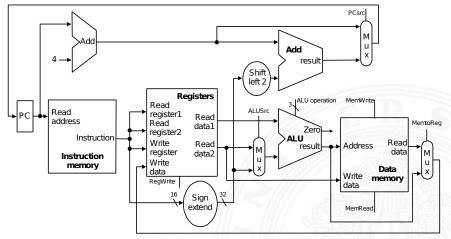

## MIPS: serielle Realisierung ohne Pipeline

Pipelining - MIPS Rechnerarchitektur

längster Pfad: PC - IM - REG - MUX - ALU - DM - MUX - PC/REG [PH20]

◆ RISC Pipelining

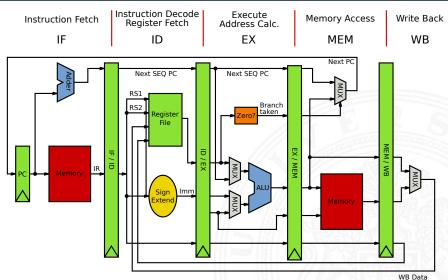

## MIPS: mit 5-stufiger Pipeline

Pipelining - MIPS Rechnerarchitektur

◆ RISC Pipelining

Rechnerarchitektur

die Hardwareblöcke selbst sind unverändert

- PC, Addierer fürs Inkrementieren des PC

- ► Registerbank

- ► Rechenwerke: ALU, sign-extend, zero-check

- ► Multiplexer und Leitungen/Busse

- vier zusätzliche Pipeline-Register

- ▶ die (decodierten) Befehle

- alle Zwischenergebnisse

- alle intern benötigten Statussignale

- ▶ längster Pfad zwischen Registern jetzt eine der 5 Stufen

- aber wie wirkt sich das auf die Software aus?!

Rechnerarchitektur

Pipelining - Bewertung

#### Begriffe

- ▶ **Pipeline-Stage**: einzelne Stufe der Pipeline

- Pipeline Machine Cycle: Instruktion kommt einen Schritt in Pipeline weiter

- Durchsatz: Anzahl der Instruktionen, die in jedem Takt abgeschlossen werden

- ► Latenz: Zeit, die eine Instruktion benötigt, um alle Pipelinestufen zu durchlaufen

#### Vor- und Nachteile

- + Schaltnetze in kleinere Blöcke aufgeteilt ⇒ höherer Takt

- + im Idealfall ein neuer Befehl pro Takt gestartet  $\Rightarrow$  höherer Durchsatz, bessere Performanz

- + geringer Zusatzaufwand an Hardware

- + Pipelining ist für den Programmierer nicht direkt sichtbar!

- Achtung: Daten-/Kontrollabhängigkeiten (s.u.)

- Latenz wird nicht verbessert, bleibt bestenfalls gleich

- Pipeline Takt limitiert durch langsamste Pipelinestufe unausgewogene Pipelinestufen reduzieren den Takt und damit die Performanz

- zusätzliche Zeiten, um Pipeline zu füllen bzw. zu leeren

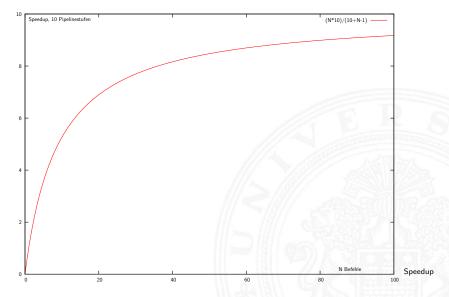

#### Analyse

- ▶ *N* Instruktionen; *K* Pipelinestufen

- ▶ ohne Pipeline: *N* · *K* Taktzyklen

- ▶ mit Pipeline: K + N 1 Taktzyklen

▶ "Speedup"

$$S = \frac{N \cdot K}{K + N - 1}$$

,  $\lim_{N \to \infty} S = K$

- ⇒ ein großer Speedup wird erreicht durch

- ▶ große Pipelinetiefe: *K*

- ▶ lange Instruktionssequenzen: N

- wegen Daten- und Kontrollabhängigkeiten nicht erreichbar

- ▶ außerdem: Register-Overhead nicht berücksichtigt

## Prozessorpipeline – Bewertung (cont.)

Pipelining - Bewertung

Rechnerarchitektur

## Prozessorpipeline - Dimensionierung

Pipelining - Bewertung

Rechnerarchitektur

- ▶ größeres K wirkt sich direkt auf den Durchsatz aus

- weniger Logik zwischen den Registern, höhere Taktfrequenzen

- ▶ zusätzlich: technologischer Fortschritt (1985...2010)

- Beispiele

| CPU                | Pipelinestufen | Taktfrequenz [MHz] |

|--------------------|----------------|--------------------|

| 80 386             | 1              | 33                 |

| Pentium            | 5              | 300                |

| Motorola G4        | 4              | 500                |

| Motorola G4e       | 7              | 1000               |

| Pentium II/III     | 12             | 1400               |

| Athlon XP          | 10/15          | 2500               |

| Athlon 64, Opteron | 12/17          | ≤ 3000             |

| Pentium 4          | 20             | ≤ 5000             |

A. Måder

Pipelining - Bewertung Rechnerarchitektur

# Architekturentscheidungen, die sich auf das Pipelining auswirken gut für Pipelining

- ▶ gleiche Instruktionslänge

- wenige Instruktionsformate

- ► Load/Store Architektur

#### BASIC INSTRUCTION FORMATS

| R | opcode |      | rs      | rt    | rd    | shamt     | funct |

|---|--------|------|---------|-------|-------|-----------|-------|

|   | 31 2   | 6 25 | 21      | 20 16 | 15 11 | 10 6      | 5 0   |

| I | opcode |      | rs      | rt    |       | immediate | •     |

|   | 31 2   | 6 25 | 21      | 20 16 | 15    |           | 0     |

| J | opcode |      | address |       |       |           |       |

|   | 21 2   | 6.25 |         |       |       |           | 0     |

#### FLOATING-POINT INSTRUCTION FORMATS

| CATING-FORT INSTRUCTION FORMATS |        |       |       |           |      |       |  |

|---------------------------------|--------|-------|-------|-----------|------|-------|--|

| FR                              | opcode | fmt   | ft    | fs        | fd   | funct |  |

|                                 | 31 26  | 25 21 | 20 16 | 15 11     | 10 6 | 5 0   |  |

| FI                              | opcode | fmt   | ft    | immediate |      | ;     |  |

|                                 | 21 26  | 25 21 | 20 16 | 15        |      | 0     |  |

MIPS-Befehlsformate [PH20]

## Prozessorpipeline – Auswirkungen (cont.)

Rechnerarchitektur

## schlecht für Pipelining: Pipelinekonflikte / -Hazards

- Strukturkonflikt: gleichzeitiger Zugriff auf eine Ressource durch mehrere Pipelinestufen

- Datenkonflikt: Ergebnisse von Instruktionen werden innerhalb der Pipeline benötigt

- Steuerkonflikt: Sprungbefehle in der Pipelinesequenz

#### sehr schlecht für Pipelining

- Unterbrechung des Programmkontexts: Interrupt, System-Call, Exception . . .

- ► (Performanz-) Optimierungen mit "Out-of-Order Execution" etc.

A. Mädei

## Pipeline Schema

Pipelining - Bewertung Rechnerarchitektu

◆ RISC Pipelining

Pipelining - Hazards Rechnerarchitektur

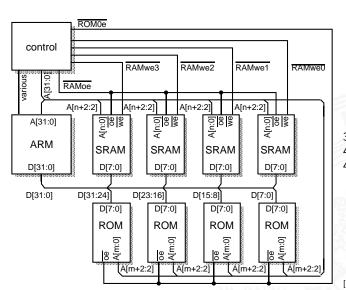

#### Strukturkonflikt / Structural Hazard

▶ mehrere Stufen wollen gleichzeitig auf eine Ressource zugreifen

▶ Beispiel

- ► Beispiel: gleichzeitiger Zugriff auf Speicher

- ⇒ Mehrfachauslegung der betreffenden Ressourcen

- ► Harvard-Architektur vermeidet Strukturkonflikt aus Beispiel

- Multi-Port Register

- mehrfach vorhandene Busse und Multiplexer . . .

## Beispiel: Strukturkonflikt

Pipelining - Hazards Rechnerarchitektur

◆ Strukturkonflikte

gleichzeitigen Laden aus einem Speicher, zwei verschiedene Adressen

Pipelining - Hazards Rechnerarchitektur

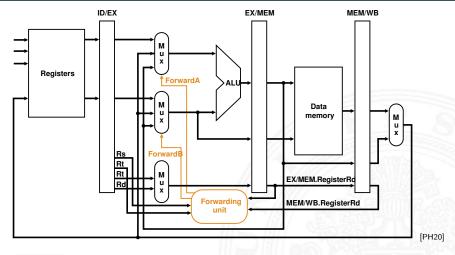

#### Datenkonflikt / Data Hazard

- eine Instruktion braucht die Ergebnisse einer vorhergehenden, diese wird aber noch in der Pipeline bearbeitet

- ► Datenabhängigkeiten aufeinanderfolgender Befehle

- ▶ Operanden während ID-Phase aus Registerbank lesen

- ▶ Resultate werden erst in WB-Phase geschrieben

- ⇒ aber: Resultat ist schon nach EX-/MEM-Phase bekannt

#### Forwarding

- zusätzliche Hardware ("Forwarding-Unit") kann Datenabhängigkeiten auflösen

- Änderungen in der Pipeline Steuerung

- neue Datenpfade und Multiplexer

▶ ohne Forwarding ▶ mit Forwarding

Beispie

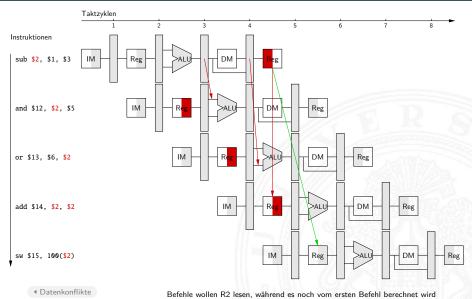

# Pipeline Datenkonflikte (cont.)

Pipelining - Hazards Rechnerarchitektur

#### Rückwärtsabhängigkeiten

spezielle Datenabhängigkeit

- ▶ Beispiel

- ► Forwarding-Technik funktioniert nicht, da die Daten erst *später* zur Verfügung stehen

- bei längeren Pipelines

- ▶ bei Load-Instruktionen (s.u.)

#### Auflösen von Rückwärtsabhängigkeiten

- Softwarebasiert, durch den Compiler, Reihenfolge der Instruktionen verändern

- ▶ Beispiel

- ▶ andere Operationen (ohne Datenabhängigkeiten) vorziehen

- nop-Befehl(e) einfügen

Pipelining - Hazards Rechnerarchitektur

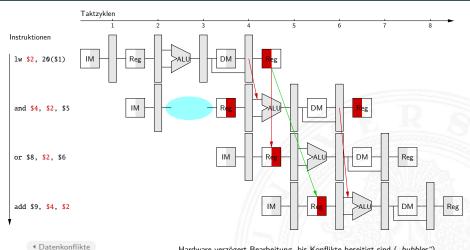

#### 2. "Interlocking"

▶ Beispiel

- zusätzliche (Hardware) Kontrolleinheit: komplexes Steuerwerk

- ▶ automatisches Stoppen der Pipeline, bis die benötigten Daten zur Verfügung stehen – Strategien:

- ▶ in Pipeline werden keine neuen Instruktionen geladen

- ► Hardware erzeugt: Pipelineleerlauf / "pipeline stall"

#### "Scoreboard"

- ► Hardware Einheit zur zentralen Hazard-Erkennung und -Auflösung

- ▶ Verwaltet Instruktionen, benutzte Einheiten und Register der Pipeline (siehe "Superskalare Rechner", ab Folie 151)

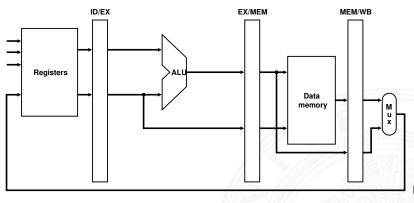

# Beispiel: MIPS Datenpfad

Pipelining - Hazards Rechnerarchitektur

◆ Forwarding

## Beispiel: MIPS Forwarding

Pipelining - Hazards

Rechnerarchitektur

◆ Forwarding

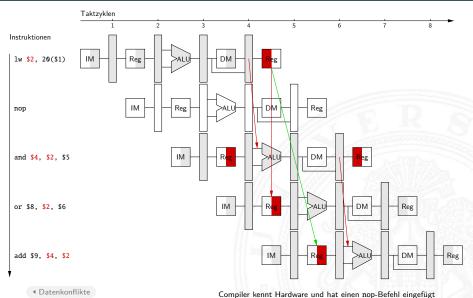

## Beispiel: Datenkonflikt

Pipelining - Hazards Rechnerarchitektur

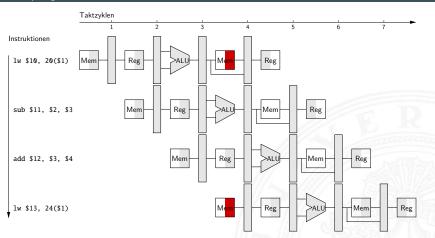

## Beispiel: Rückwärtsabhängigkeit

IM

Pipelining - Hazards

Rechnerarchitektur

Taktzyklen

Instruktionen

Iw \$2, 20(\$1)

IM Reg

ALU

DM

Reg

Reg

Rechnerarchitektur

or \$8, **\$2**, \$6

add \$9, \$4, \$2

◆ Datenkonflikte

Befehle wollen R2 lesen, bevor es aus Speicher geladen wird

DM

Reg

Reg

Pipelining - Hazards Rechnerarchitektur

Pipelining - Hazards Rechnerarchitektur

A. Mäder

Hardware verzögert Bearbeitung, bis Konflikte beseitigt sind ("bubbles")

Pipelining - Hazards Rechnerarchitektur

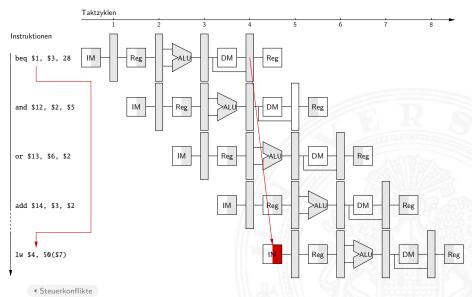

#### Steuerkonflikt / Control Hazard

- ► Unterbrechung des sequenziellen Ablaufs durch

Sprungbefehle und Unterprogrammaufrufe: call und ret

- Instruktionen die auf (bedingte) Sprünge folgen, werden bereits in die Pipeline geschoben

- Sprungadresse und Status (taken/untaken) sind aber erst am Ende der EX-Phase bekannt

- einige Befehle wurden bereits teilweise ausgeführt, Resultate eventuell "ge-forwarded"

- alle Zwischenergebnisse müssen verworfen werden

- ▶ inklusive aller Forwarding-Daten

- ▶ Pipeline an korrekter Zieladresse neu starten

- erfordert sehr komplexe Hardware

- jeder (ausgeführte) Sprung kostet enorm Performanz

## Pipeline Steuerkonflikte (cont.)

Pinelining - Hazards

#### Lösungsmöglichkeiten für Steuerkonflikte

- ▶ ad-hoc Lösung: "Interlocking" Pipeline prinzipiell bei Sprüngen leeren

- ineffizient: ca. 19 % der Befehle sind Sprünge

- 1. Annahme: (nicht) ausgeführter Sprung "(un)taken branch"

- + kaum zusätzliche Hardware

- im Fehlerfall muss Pipeline geleert werden "flush instructions"

Rechnerarchitektur

- 2. Sprungentscheidung "vorverlegen"

- ► Software: Compiler zieht andere Instruktionen vor Verzögerung nach Sprungbefehl "delay slots"

- Hardware: Sprungentscheidung durch Zusatz-ALU (nur Vergleiche) während Befehlsdecodierung (z.B. MIPS)

Pipelining - Hazards Rechnerarchitektur

### 3. Sprungvorhersage

"branch prediction"

- ► Beobachtung: ein Fall tritt häufiger auf; Schleifendurchlauf, Datenstrukturen durchsuchen etc.

- mehrere Vorhersageverfahren; oft miteinander kombiniert

- + hohe Trefferquote: bis 90 %

### Statische Sprungvorhersage (softwarebasiert)

- Compiler erzeugt extra Bit in Opcode des Sprungbefehls

- Methoden: Codeanalyse, Profiling . . .

### Dynamische Sprungvorhersage (hardwarebasiert)

- ► Sprünge durch Laufzeitinformation vorhersagen: Wie oft wurde der Sprung in letzter Zeit ausgeführt?

- viele verschiedene Verfahren:

History-Bit, 2-Bit Prädiktor, korrelationsbasierte Vorhersage,

Branch History Table, Branch Target Cache . . .

Pipelining - Hazards Rechnerarchitektur

- ► Schleifen abrollen / "Loop unrolling"

- ▶ zusätzliche Maßnahme zu allen zuvor skizzierten Verfahren

- bei statischer Schleifenbedingung möglich

- ► Compiler iteriert Instruktionen in der Schleife (teilweise)

- längerer Code

- + Sprünge und Abfragen entfallen

- + erzeugt sehr lange Codesequenzen ohne Sprünge

- ⇒ Pipeline kann optimal ausgenutzt werden

# Beispiel: Steuerkonflikt

Pipelining - Hazards Rechnerarchitektur

Pipelining - Hazards Rechnerarchitektur

- von-Neumann Zyklus auf separate Phasen aufteilen

- ▶ überlappende Ausführung von mehreren Befehlen

- ▶ einfachere Hardware für jede Phase ⇒ höherer Takt

- ▶ mehrere Befehle in Bearbeitung ⇒ höherer Durchsatz

- ► 5-stufige RISC-Pipeline: IF→ID/OF→Exe→Mem→WB

- ▶ mittlerweile sind 9...20 Stufen üblich

- ► Struktur-, Daten- und Steuerkonflikte

- ► Lösung durch mehrfache/bessere Hardware

- ▶ Data-Forwarding umgeht viele Datenabhängigkeiten

- Sprungbefehle sind ein ernstes Problem

- ▶ Pipelining ist prinzipiell unabhängig von der ISA

- einige Architekturen basiseren auf Pipelining (MIPS)

- ► Compiler/Tools/Progammierer sollten CPU Pipeline kennen

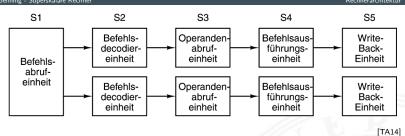

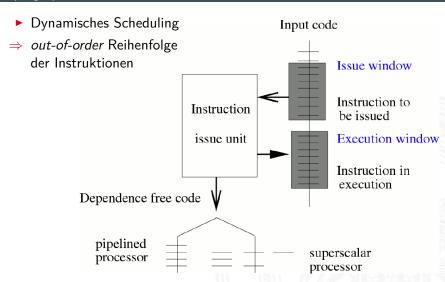

Pipelining - Superskalare Rechner Rechnerarchitektur

▶ Befehl in kleinere, schnellere Schritte aufteilen ⇒ höherer Takt

▶ mehrere Instruktionen überlappt ausführen ⇒ höherer Durchsatz

- ▶ im Bild jeweils zwei Operationen pro Pipelinestufe

- ▶ parallele ("superskalare") Ausführung

- komplexe Hardware (Daten- und Kontrollabhängigkeiten)

- ▶ Beispiel: Pentium

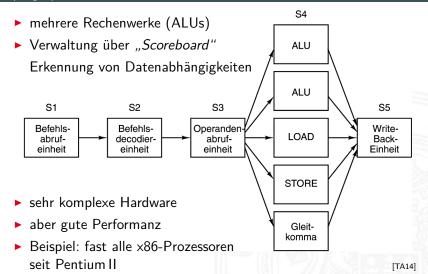

# Superskalarer Prozessor

Pipelining - Superskalare Rechner

Rechnerarchitektur

Pipelining - Superskalare Rechner

- ► Superskalare CPUs besitzen mehrere Recheneinheiten: 4...10

- ▶ in jedem Takt werden (dynamisch) mehrere Instruktionen eines konventionell linearen Instruktionsstroms abgearbeitet

- ⇒ ILP (Instruction Level Parallelism)

- ▶ Hardware verteilt initiierte Instruktionen auf Recheneinheiten

- pro Takt kann mehr als eine Instruktion initiiert werden

Die Anzahl wird dynamisch von der Hardware bestimmt:

0..., Instruction Issue Bandwidth"

- + sehr effizient, alle modernen CPUs sind superskalar

- Abhängigkeiten zwischen Instruktionen sind der Engpass, das Problem der Hazards wird verschärft

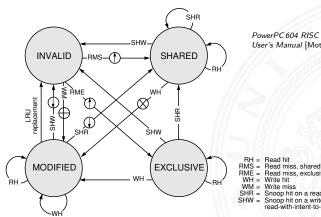

#### Datenabhängigkeiten

- ► RAW Read After Write Instruktion I<sub>x</sub> darf Datum erst lesen, wenn I<sub>x-n</sub> geschrieben hat

- ► WAR Write After Read Instruktion I<sub>x</sub> darf Datum erst schreiben, wenn I<sub>x-n</sub> gelesen hat

- ▶ WAW Write After Write Instruktion  $I_x$  darf Datum erst überschreiben, wenn  $I_{x-n}$  geschrieben hat

#### Datenabhängigkeiten superskalarer Prozessoren

- ► RAW: echte Abhängigkeit; Forwarding ist kaum möglich und in superskalaren Pipelines extrem aufwändig

- ▶ WAR, WAW: "Register Renaming" als Lösung

Pipelining - Superskalare Rechner

Rechnerarchitektur

## "Register Renaming"

- Hardware löst Datenabhängigkeiten innerhalb der Pipeline auf

- ► Zwei Registersätze sind vorhanden

- 1. Architektur-Register: "logische Register" der ISA

- 2. viele Hardware-Register: "Rename Register"

- dynamische Abbildung von ISA- auf Hardware-Register

#### Beispiel

Parallelisierung des modifizierten Codes

```

tmp1 = a + b; tmp2 = d + e; res1 = c + tmp1; res2 = tmp2 - f; tmp = tmp2;

```

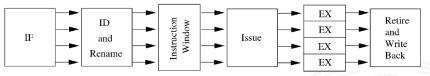

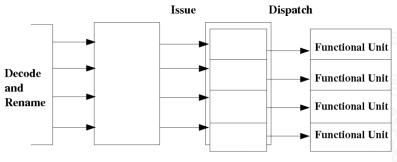

#### Aufbau der superskalaren Pipeline

- Iange Pipelines mit vielen Phasen: Fetch (Prefetch, Predecode), Decode / Register-Renaming, Issue, Dispatch, Execute, Retire (Commit, Complete / Reorder), Write-Back

- ▶ je nach Implementation unterschiedlich aufgeteilt

- ▶ entscheidend für superskalare Architektur sind die Schritte

vor den ALUs: Issue, Dispatch ⇒ out-of-order Ausführung

nach -"- : Retire ⇒ in-order Ergebnisse

# Superskalar – Pipeline (cont.)

Pipelining - Superskalare Rechner

Rechnerarchitektur

Rechnerarchitektur

Pipelining - Superskalare Rechner

Issue: globale Sicht Dispatch: getrennte Ausschnitte in "Reservation Stations"

**Reservation Stations**

- Reservation Station für jede Funktionseinheit

- ▶ speichert: initiierte Instruktionen die auf Recheneinheit warten

- –"– zugehörige Operanden

- –"– ggf. Zusatzinformation

- ► Instruktion bleibt blockiert, bis alle Parameter bekannt sind und wird dann an die zugehörige ALU weitergeleitet

- ▶ ggf. "Retire"-Stufe

- ▶ Reorder-Buffer: erzeugt wieder *in-order* Reihenfolge

- commit: "richtig ausgeführte" Instruktionen gültig machen abort: Instruktionen verwerfen, z.B. Sprungvorhersage falsch

- Dynamisches Scheduling: zuerst '67 in IBM 360 (R. Tomasulo)

- Forwarding

- Registerumbenennung und Reservation Stations

### Spezielle Probleme superskalarer Pipelines

- weitere Hazard-Möglichkeiten

- die verschiedenen ALUs haben unterschiedliche Latenzzeiten.

- Befehle ..warten" in den Reservation Stations

- ⇒ Datenabhängigkeiten können sich mit jedem Takt ändern

- Kontrollflussabhängigkeiten: Anzahl der Instruktionen zwischen bedingten Sprüngen limitiert Anzahl parallelisierbarer Instruktionen

- ⇒ "Loop Unrolling" besonders wichtig

- + optimiertes (dynamisches) Scheduling: Faktor 3 möglich

Pipelining - Superskalare Rechner

Rechnerarchitektur

Softwareunterstützung für Pipelining superskalarer Prozessoren "Software Pipelining"

- Codeoptimierungen beim Compilieren als Ersatz/Ergänzung zur Pipelineunterstützung durch Hardware

- ► Compiler hat "globalen" Überblick

- ⇒ zusätzliche Optimierungsmöglichkeiten

Rechnerarchitektur

Pipelining - Superskalare Rechner

### Interrupts, System-Calls und Exceptions

- ▶ Pipeline kann normalen Ablauf nicht fortsetzen

- Ausnahmebehandlung ist wegen der Vielzahl paralleler Aktionen und den Abhängigkeiten innerhalb der Pipelines extrem aufwändig

- einige Anweisungen können verworfen werden

- andere Pipelineaktionen müssen vollendet werden benötigt zusätzliche Zeit bis zur Ausnahmebehandlung

- wegen Register-Renaming muss viel mehr Information gerettet werden als nur die ISA-Register

## Prinzip der Interruptbehandlung

- keine neuen Instruktionen mehr initiieren

- warten bis Instruktionen des Reorder-Buffers abgeschlossen sind

- ▶ Verfahren ist von der "Art" des Interrupt abhängig

- ► Precise-Interrupt: Pipelineaktivitäten komplett Beenden

- Imprecise-Interrupt: wird als verzögerter Sprung (Delayed-Branching) in Pipeline eingebracht

Zusätzliche Register speichern Information über Instruktionen die in der Pipeline nicht abgearbeitet werden können (z.B. weil sie den Interrupt ausgelöst haben)

- Definition: Precise-Interrupt

- ▶ Programmzähler (PC) zur auslösenden Instruktion ist bekannt

- ▶ alle Instruktionen bis zur PC-Instr. wurden vollständig ausgeführt

- ▶ keine Instruktion nach der PC-Instr. wurde ausgeführt

- Ausführungszustand der PC-Instruktion ist bekannt

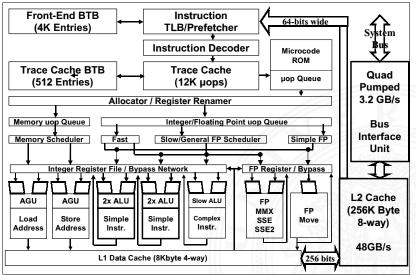

- superskalare Architektur (mehrere ALUs)

- ▶ CISC-Befehle werden dynamisch in " $\mu$ OPs" (1...3) umgesetzt

- lacktriangle Ausführung der  $\mu$ OPs mit "Out of Order" Maschine, wenn

- Operanden verfügbar sind

- ► funktionelle Einheit (ALU) frei ist

- ► Ausführung wird durch "Reservation Stations" kontrolliert

- $\blacktriangleright$  beobachtet die Datenabhängigkeiten zwischen  $\mu \mathsf{OPs}$

- ▶ teilt Ressourcen zu

- ▶ "Trace" Cache

- ersetzt traditionellen Anweisungscache

- speichert Anweisungen in decodierter Form: Folgen von  $\mu OPs$

- reduziert benötigte Rate für den Anweisungsdecoder

- "Double pumped" ALUs (2 Operationen pro Taktzyklus)

Pipelining - Superskalare Rechner

Rechnerarchitektur

▶ große Pipelinelänge ⇒ sehr hohe Taktfrequenzen

| Basic Pentium III Processor Misprediction Pipeline |       |                        |        |        |        |        |         |          |      |

|----------------------------------------------------|-------|------------------------|--------|--------|--------|--------|---------|----------|------|

| 1                                                  | 2     | 3<br>Decode            | 4      | 5      | 6      | 7      | 8       | 9        | 10   |

| Fetch                                              | Fetch | Decode                 | Decode | Decode | Rename | ROB Rd | Rdy/Sch | Dispatch | Exec |

|                                                    |       |                        |        |        |        |        |         |          |      |

|                                                    |       | ntium                  |        |        |        |        |         | 1        |      |

|                                                    |       | ntium  5 6 Drive Alloc |        |        |        |        |         | 1        |      |

umfangreiches Material von Intel unter: ark.intel.com, www.intel.com

# Beispiel: Pentium 4 / NetBurst Architektur (cont.)

Pipelining - Superskalare Rechner

Rechnerarchitektur

Figure 4: Pentium® 4 processor microarchitecture

Intel: Q1, 2001

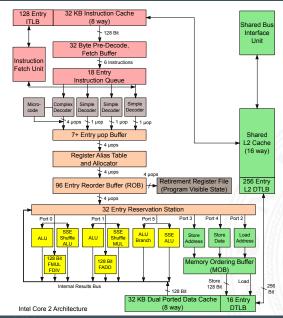

## Beispiel: Core 2 Architektur

Pipelining - Superskalare Rechner

Rechnerarchitektur

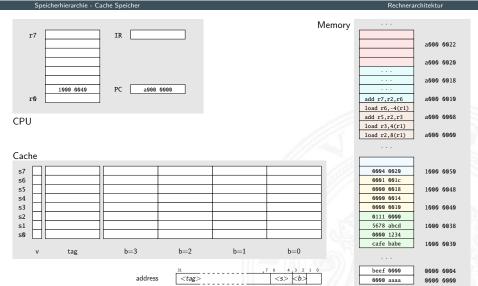

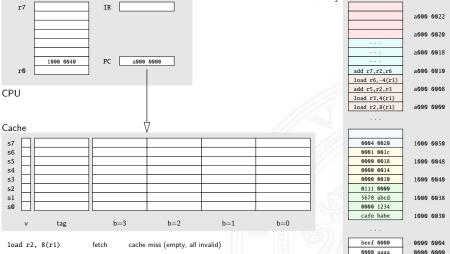

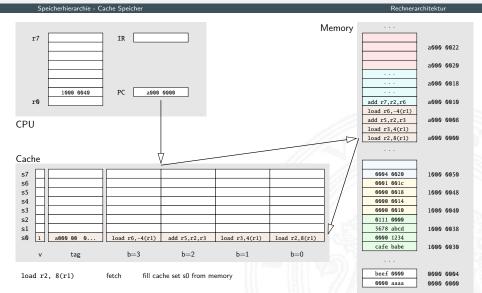

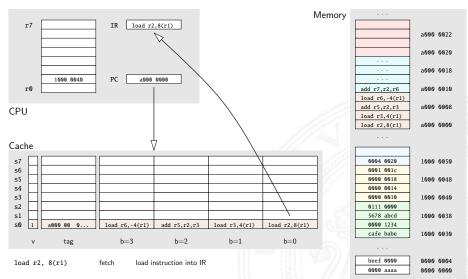

Speicherhierarchie

- 1. Rechnerarchitektur

- 2. Bewertung von Architekturen und Rechnersystemen

- 3. Instruction Set Architecture

- 4. Pipelining

- 5. Speicherhierarchie

Speichertypen

Halbleiterspeicher

spezifische Eigenschaften

Motivation

Cache Speicher

Virtueller Speicher

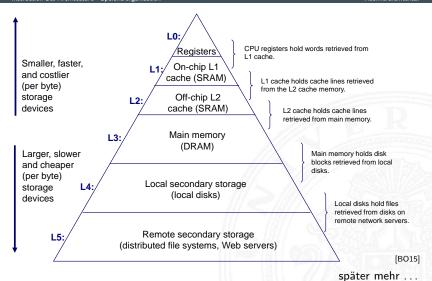

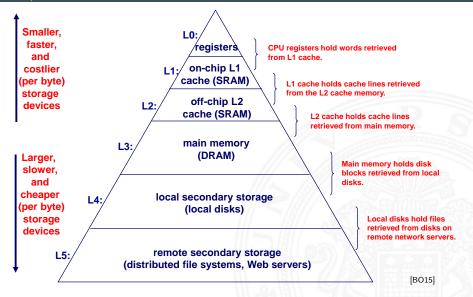

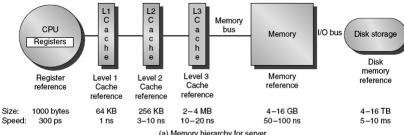

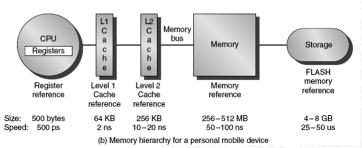

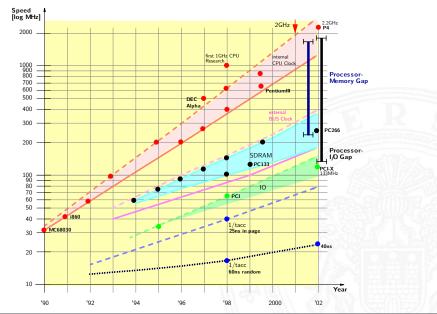

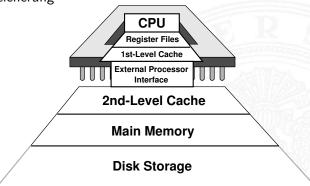

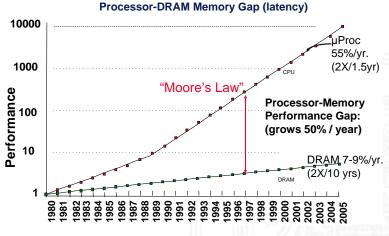

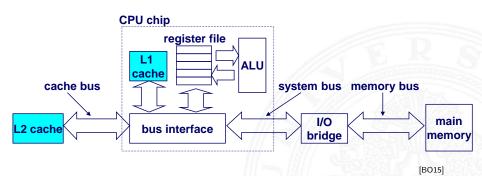

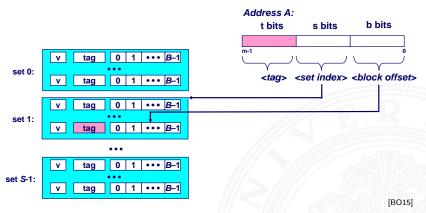

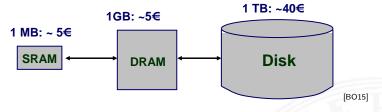

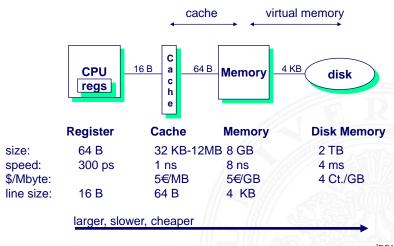

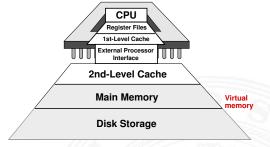

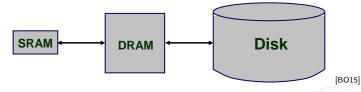

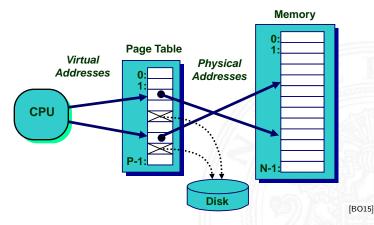

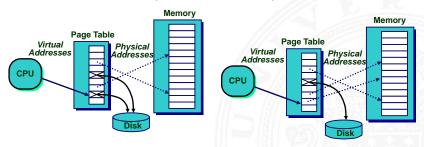

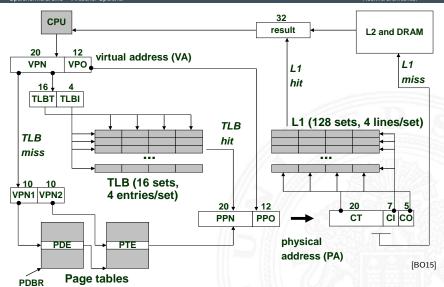

# Speicherhierarchie: Konzept

Speicherhierarchie Rechnerarchitektur

peicherhierarchie Rechnerarchitektur

### Gesamtsystem kombiniert verschiedene Speicher

- wenige KByte Register (-bank) im Prozessor

- einige MByte SRAM als schneller Zwischenspeicher

- einige GByte DRAM als Hauptspeicher

- einige TByte Festplatte als nichtflüchtiger Speicher

- ► Hintergrundspeicher (CD/DVD/BR, Magnetbänder)

- das WWW und Cloud-Services

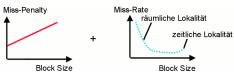

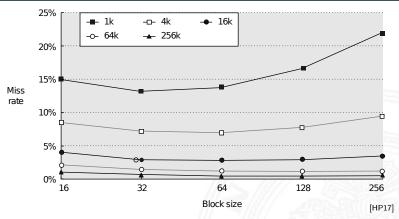

#### Kompromiss aus Kosten, Kapazität, Zugriffszeit

- ▶ Illusion aus großem schnellem Speicher

- ▶ funktioniert nur wegen räumlicher/zeitlicher Lokalität

Speicherhierarchie - Speichertypen

- Register im Prozessor integriert

- ▶ Program-Counter und Datenregister für Programmierer sichtbar

- ▶ ggf. weitere Register für Systemprogrammierung

- zusätzliche unsichtbare Register im Steuerwerk

- ► Flipflops oder Registerbank mit 6 Trans.-Speicherzellen

- Lesen und Schreiben in jedem Takt möglich

- ggf. mehrere parallele Lesezugriffe in jedem Takt

- Zugriffszeiten ca. 100 ps

- ▶ typ. Größe einige KByte, z.B. 16 Register á 64-bit

x86-64

Speicherhierarchie - Speichertyper

Rechnerarchitektur

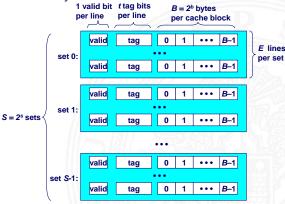

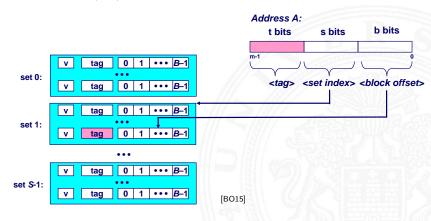

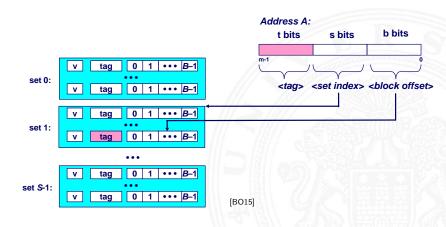

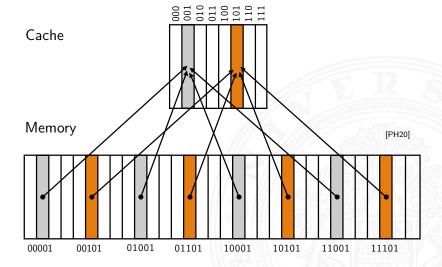

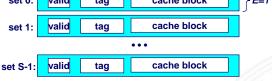

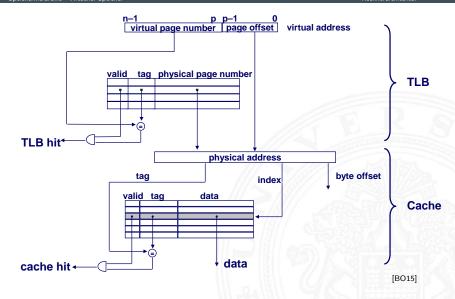

- ▶ "Random-Access Memory" (RAM) aufgebaut aus Mikrochips

- Grundspeichereinheit ist eine Zelle (ein Bit pro Zelle)