# 64-040 Modul InfB-RSB Rechnerstrukturen und Betriebssysteme

https://tams.informatik.uni-hamburg.de/ lectures/2023ws/vorlesung/rsb

- Kapitel 11 -

#### Andreas Mäder

Universität Hamburg Fakultät für Mathematik, Informatik und Naturwissenschaften

Fachbereich Informatik

Technische Aspekte Multimodaler Systeme

Wintersemester 2023/2024

### Rechnerarchitektur I

Motivation

von-Neumann Rechner

Beschreibungsebenen

Software

HW Abstraktionsebenen

Hardwarestruktur

Speicherbausteine

Busse

Mikroprogrammierung

Beispielsystem: ARM

Wie rechnet ein Rechner?

Literatur

#### Definitionen

- The term architecture is used here to describe the attributes of a system as seen by the programmer, i.e., the conceptual structure and functional behaviour, as distinct from the organization and data flow and control, the logical and the physical implementation.

[Amdahl, Blaauw, Brooks]

- 2. The study of computer architecture is the study of the organization and interconnection of components of computer systems. Computer architects construct computers from basic building blocks such as memories, arithmetic units and buses. From these building blocks the computer architect can construct anyone of a number of different types of computers, ranging from the smallest hand-held pocket-calculator to the largest ultra-fast super computer. The functional behaviour of the components of one computer are similar to that of any other computer, whether it be ultra-small or ultra-fast.

11.1 Rechnerarchitektur I - Motivation

By this we mean that a memory performs the storage function, an adder does addition, and an input/output interface passes data from a processor to the outside world, regardless of the nature of the computer in which they are embedded. The major differences between computers lie in the way of the modules are connected together, and the way the computer system is controlled by the programs. In short, computer architecture is the discipline devoted to the design of highly specific and individual computers from a collection of common building blocks. [Stone]

11.1 Rechnerarchitektur I - Motivation

- Operationsprinzip: das funktionelle Verhalten der Architektur

- = Programmierschnittstelle

- ISA Instruction Set Architecture Befehlssatzarchitektur

- Maschinenorganisation: Wie werden Befehle abgearbeitet?

- → folgt ab Kapitel 12 Instruction Set Architecture

- Hardwarearchitektur: der strukturelle Aufbau des Rechnersystems

- Art und Anzahl der Hardware-Betriebsmittel + die Verbindungs- / Kommunikationseinrichtungen

- = (technische) Implementierung

Befehlssatz

Mikroarchitektur

- ▶ J. Mauchly, J.P. Eckert, J. von-Neumann 1945

- Abstrakte Maschine mit minimalem Hardwareaufwand

- ▶ System mit Prozessor, Speicher, Peripheriegeräten

- die Struktur ist unabhängig von dem Problem, das Problem wird durch austauschbaren Speicherinhalt (Programm) beschrieben

- gemeinsamer Speicher für Programme und Daten

- fortlaufend adressiert

- ▶ Programme können wie Daten manipuliert werden

- ▶ Daten können als Programm ausgeführt werden

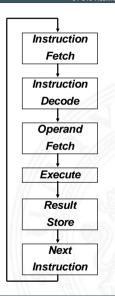

- ▶ Befehlszyklus: Befehl holen, decodieren, ausführen

- ⇒ enorm flexibel

- ▶ alle aktuellen Rechner basieren auf diesem Prinzip

- ▶ aber vielfältige Architekturvarianten, Befehlssätze usw.

- Programm als Sequenz elementarer Anweisungen (Befehle)

- ▶ als Bitvektoren im Speicher codiert

- ▶ Interpretation (Operanden, Befehle und Adressen) ergibt sich aus dem Kontext (der Adresse)

- zeitsequenzielle Ausführung der Instruktionen

- Ausführungszyklus

- 1. Befehl aus Programmspeicher holen

- auszuführende Aktionen und Länge der Instruktion bestimmen, ggf. Worte nachladen

- 3. Operanden ermitteln und laden

- 4. Ergebnis der Operation berechnen bzw. Status ermitteln

- 5. Ergebnisse für später abspeichern

- 6. Folgeoperation ermitteln

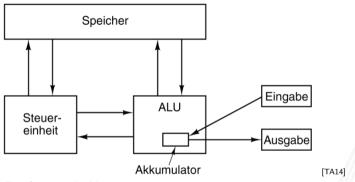

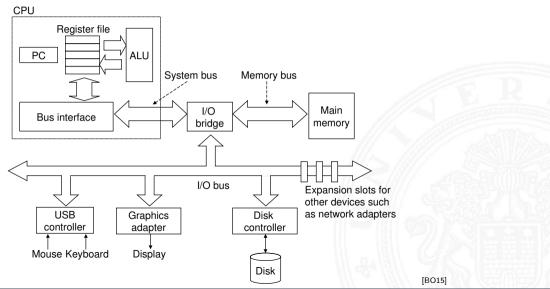

Fünf zentrale Komponenten:

- ► Prozessor mit Steuerwerk und Rechenwerk (ALU, Register)

- ▶ Speicher, gemeinsam genutzt für Programme und Daten

- ► Eingabe- und Ausgabewerke

- verbunden durch Bussystem

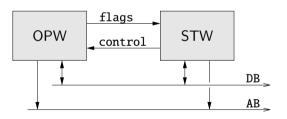

- ▶ Prozessor (CPU) = Steuerwerk + Operationswerk

- ► Steuerwerk: zwei zentrale Register

- ▶ Befehlszähler (*PC program counter*)

- ▶ Befehlsregister (*IR* instruction register)

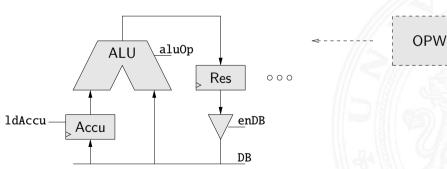

- Operationswerk (Datenpfad data-path)

- ► Rechenwerk (ALU arithmetic-logic unit)

- ▶ Universalregister (8...64 Register, mind. 1 Akkumulator)

- evtl. Register mit Spezialaufgaben

- Speicher (memory)

- ► Hauptspeicher/RAM: random-access memory

- ► Hauptspeicher/ROM: read-only memory zum Booten

- externer Speicher (Virtual Memory): Festplatten, CD/DVD, Bandarchiv, Netzwerk

- ► Peripheriegeräte: Ein-/Ausgabe (I/O)

11.2 Rechnerarchitektur I - von-Neumann Rechner

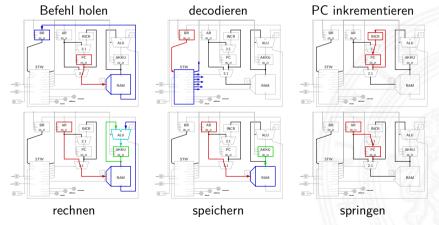

- ▶ Verschaltung der Hardwarekomponenten für alle mögl. Datentransfers

- ▶ abhängig vom Befehl werden nur bestimmte Pfade aktiv

- Ausführungszyklus

11.3 Rechnerarchitektur I - Beschreibungsebenen

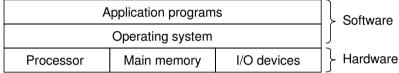

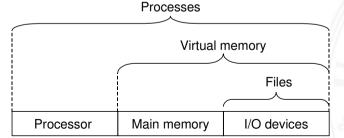

► Schichten-Ansicht: Software – Hardware

[BO15]

► Abstraktionen durch Betriebssystem

[BO15]

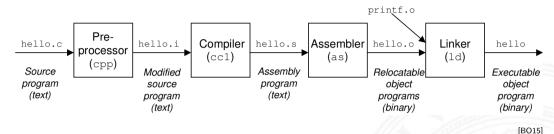

11.3.1 Rechnerarchitektur I - Beschreibungsebenen - Software

- verschiedene Repräsentationen des Programms

- ► Hochsprache

- Assembler

- Maschinensprache

- Ausführung der Maschinensprache

- von-Neumann Zyklus: Befehl holen, decodieren, ausführen

- reale oder virtuelle Maschine

```

High Level Language Program

Compiler

Assembly Language Program

```

Assembler

Machine Language Program

```

temp = v[k];

```

v[k] = v[k+1];

v[k+1] = temp;

lw \$15, 0(\$2)

lw \$16, 4(\$2)

sw \$16, 0(\$2)

sw \$15, 4(\$2)

0000 1001 1100 0110 1010 1111 0101 1000 1001 1111 0101 1000 0100 1001 1100 0110 1100 0110 1100 0110 1000 0000 1001 1001 1000 0000 1001 1001 1000 0000 1001

## Machine Interpretation

Control Signal Specification

ALUOP[0:3] <= InstReg[9:11] & MASK

[PH22]

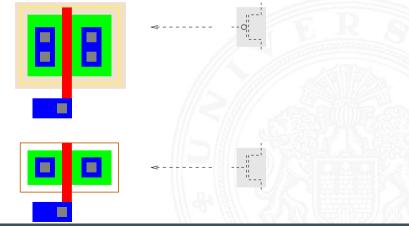

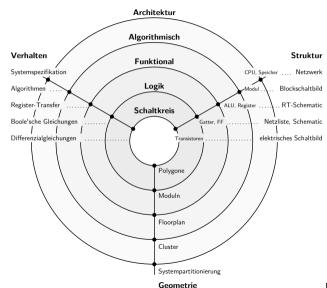

### Hardware Abstraktionsebenen

- keine einheitliche Bezeichnung in der Literatur

- Architekturebene

- ► Funktion/Verhalten Leistungsanforderungen

- Struktur

aus

Netzwerk

Prozessoren, Speicher, Busse, Controller . . .

- ► Nachrichten Programme, Prokolle

- ► Geometrie Systempartitionierung

11.3.2 Rechnerarchitektur I - Beschreibungsebenen - HW Abstraktionsebenen

► Hauptblockebene (Algorithmenebene, funktionale Ebene)

► Funktion/Verhalten Algorithmen, formale Funktionsmodelle

Struktur Blockschaltbild

aus Hardwaremodule, Busse . . .

► Nachrichten Prokolle

Geometrie Cluster

11.3.2 Rechnerarchitektur I - Beschreibungsebenen - HW Abstraktionsebenen

► Register-Transfer Ebene

► Funktion/Verhalten Daten- und Kontrollfluss, Automaten . . .

► Struktur RT-Diagramm

aus Register, Multiplexer, ALUs . . .

Nachrichten Zahlencodierungen, Binärworte . . .

Geometrie Floorplan

$11.3.2 \ {\sf Rechnerarchitektur\,I-Beschreibungsebenen-HW\ Abstraktionsebenen}$

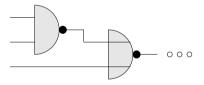

► Logikebene (Schaltwerkebene)

► Funktion/Verhalten Boole'sche Gleichungen

► Struktur Gatternetzliste, Schematic aus Gatter, Flipflops, Latches . . .

Nachrichten Bit

► Geometrie Moduln

11.3.2 Rechnerarchitektur I - Beschreibungsebenen - HW Abstraktionsebenen

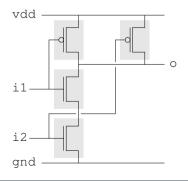

elektrische Ebene (Schaltkreisebene)

► Funktion/Verhalten Differentialgleichungen

Struktur elektrisches Schaltbildaus Transistoren, Kondensatoren . . .

Nachrichten Ströme, Spannungen

lackbox Geometrie Polygone, Layout ightarrow physikalische Ebene

11.3.2 Rechnerarchitektur I - Beschreibungsebenen - HW Abstraktionsebenen

- physikalische Ebene (geometrische Ebene)

- ► Funktion/Verhalten partielle DGL

- ► Struktur Dotierungsprofile

#### 11.3.2 Rechnerarchitektur I - Beschreibungsebenen - HW Abstraktionsebenen

#### drei unterschiedliche Aspekte/Dimensionen:

- 1 Verhalten

- 2 Struktur (logisch)

- 3 Geometrie (physikalisch)

- Start möglichst abstrakt, als Verhaltensbeschreibung

- ► Ende des Entwurfsprozesses ist das vollständige IC Layout für die Chipfertigung, Prüfmuster für Tests auf Fertigungsfehler oder Sebsttestmechanismen im IC . und die (erfolgreich) simulierte Netzliste mit Gatter- und Leitungsverzögerungen

- ... und die (erfolgreich) simulierte Netzliste mit Gatter- und Leitungsverzogerungen

- ► Entwurfsprogramme ("EDA", *Electronic Design Automation*) dabei notwendig: setzen Verhalten in Struktur und Struktur in Geometrien um, . . .

#### 11.4 Rechnerarchitektur I - Hardwarestruktur

## Modellierung eines digitalen Systems als Schaltung aus

- speichernden Komponenten

- ▶ Registern: Flipflops, Register, Registerbank . . .

- ► Speichern: SRAM, DRAM, ROM, PLA ...

- ▶ funktionalen Schaltnetzen

- ► Addierer, arithmetische Schaltungen

- ► logische Operationen

- "random-logic" Schaltnetzen

- Verbindungsleitungen

- Busse / Leitungsbündel

- Multiplexer und Tri-state Treiber

11.4 Rechnerarchitektur I - Hardwarestruktur

- bis jetzt

- ► Gatter und Schaltnetze

- ▶ Flipflops als einzelne Speicherglieder

- Schaltwerke zur Ablaufsteuerung

- ▶ weitere Komponenten: Register-Transfer- und Hauptblockebene

- Speicher

- ▶ Busse, Bustiming

- Mikroprogrammierung zur Ablaufsteuerung

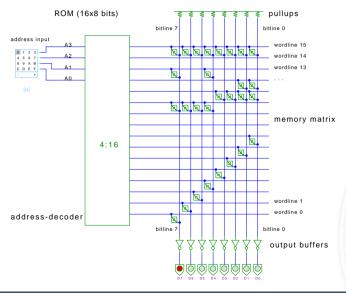

- ► System zur Speicherung von Information

- ▶ als Feld von *N* Adressen mit je *m*-bit Speicherworten

- ▶ typischerweise mit *n*-bit Adressen und  $N = 2^n$

- ▶ Kapazität also  $2^n \cdot m$  Bits

- Klassifikation

- Speicherkapazität?

- Schreibzugriffe möglich?

- Schreibzugriffe auf einzelne Bits/Bytes oder nur Blöcke?

- Information flüchtig oder dauerhaft gespeichert?

- ► Zugriffszeiten beim Lesen und Schreiben

- ► Technologie

# Speicherbausteine: Varianten

11.4.1 Rechnerarchitektur I - Hardwarestruktur - Speicherbausteine

64-040 Rechnerstrukturen und Betriebssysteme

|  |        |                 |            | byte-        |          | Typische                               |

|--|--------|-----------------|------------|--------------|----------|----------------------------------------|

|  | Тур    | Kategorie       | Löschen    | adressierbar | flüchtig | Anwendung                              |

|  | SRAM   | Lesen/Schreiben | elektrisch | ja           | ja       | Cache Speicher                         |

|  | DRAM   | Lesen/Schreiben | elektrisch | ja           | ja       | Hauptspeicher (alt)                    |

|  | SDRAM  | Lesen/Schreiben | elektrisch | ja           | ja       | Hauptspeicher                          |

|  | ROM    | nur Lesen       | _          | nein         | nein     | Embedded                               |

|  |        |                 |            |              | 1        | (große Stückzahlen)                    |

|  | PROM   | nur Lesen       | _          | nein         | nein     | Embedded                               |

|  |        |                 |            |              |          | (kleine Stückzahlen)                   |

|  | EPROM  | vorw. Lesen     | UV-Licht   | nein         | nein     | Prototypen                             |

|  | EEPROM | vorw. Lesen     | elektrisch | ja           | nein     | Prototypen                             |

|  | Flash  | Lesen/Schreiben | elektrisch | nein         | nein     | Speicherkarten, SSDs,<br>Mobile Geräte |

|  |        |                 |            |              |          |                                        |

$16 \times 8$  bit 4-bit Adresse 8-bit Datenwort

[HenHA] Hades Demo: 40-memories/20-rom/rom

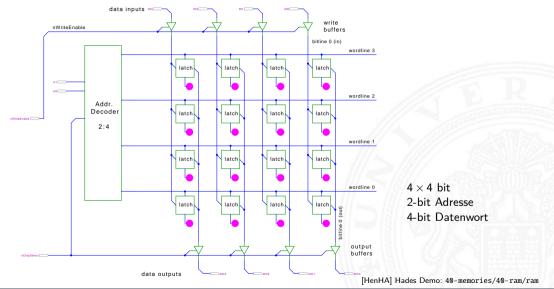

### Speicher, der im Betrieb gelesen und geschrieben werden kann

- Arbeitsspeicher des Rechners

- ▶ für Programme und Daten

- keine Abnutzungseffekte

- benötigt Spannungsversorgung zum Speichern

- Aufbau als Matrixstruktur

- ▶ *n* Adressbits, konzeptionell 2<sup>n</sup> Wortleitungen

- ▶ m Bits pro Wort

- ▶ Realisierung der einzelnen Speicherstellen?

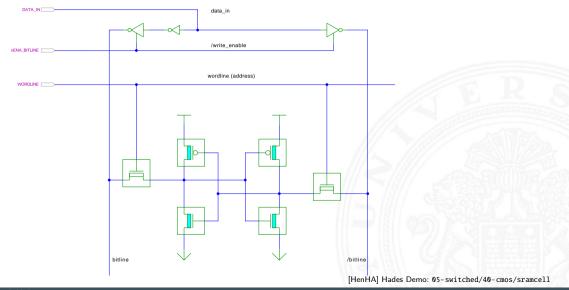

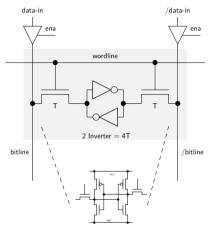

- ▶ statisches RAM: 6-Transistor Zelle ⇒ SRAM

- ▶ dynamisches RAM: 1-Transistor Zelle ⇒ DRAM

Furber: ARM SoC Architecture [Fur00]

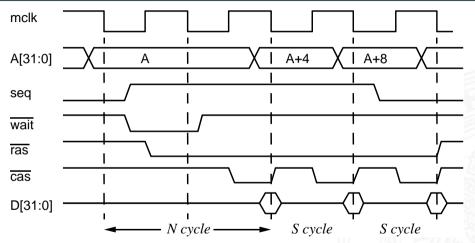

▶ Aufteilen der Adresse in zwei Hälften

cas

- ► ras "row address strobe" wählt "Wordline" cas "column address strobe" –"– "Bitline"

- ▶ je ein  $2^{(n/2)}$ -bit Decoder/Mux statt ein  $2^n$ -bit Decoder

Out

- ▶ Inhalt bleibt gespeichert solange Betriebsspannung anliegt

- sechs-Transistor Zelle zur Speicherung

- weniger Platzverbrauch als Latches/Flipflops

- kompakte Realisierung in CMOS-Technologie (s.u.)

- zwei rückgekoppelte Inverter zur Speicherung

- zwei n-Kanal Transistoren zur Anbindung an die Bitlines

- schneller Zugriff: Einsatz für Caches

- deutlich höherer Platzbedarf als DRAMs

# SRAM: Sechs-Transistor Speicherstelle ("6T")

11.4.1 Rechnerarchitektur I - Hardwarestruktur - Speicherbausteine

64-040 Rechnerstrukturen und Betriebssysteme

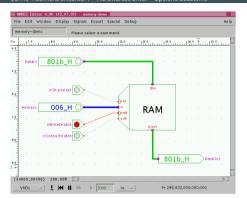

- ▶ nur aktiv wenn nCS = 0 (chip select)

- ▶ Schreiben wenn nWE = 0 (write enable)

- Ausgabe wenn nOE = 0 (output enable)

- ▶ integrierte Schaltung, 16 Ki bit Kapazität

- ▶ Organisation als 2 Ki Worte mit je 8-bit

- ▶ 11 Adresseingänge (A10...A0)

- 8 Anschlüsse für Tristate Daten-Eingang/-Ausgang

- 3 Steuersignale

- ▶  $\overline{CS}$  chip-select: Speicher nur aktiv wenn  $\overline{CS} = 0$

- $ightharpoonup \overline{WE}$  write-enable: Daten an gewählte Adresse schreiben

- ▶  $\overline{OE}$  output-enable: Inhalt des Speichers ausgeben

- ► Hades-Demo zum Ausprobieren [HenHA]

- ► Hades Demo: 40-memories/40-ram/demo-6116

- ► Hades Demo: 40-memories/40-ram/two-6116

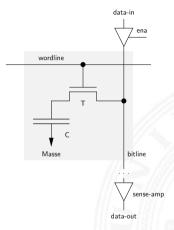

- ▶ Information wird in winzigen Kondensatoren gespeichert

- pro Bit je ein Transistor und Kondensator

- jeder Lesezugriff entlädt den Kondensator

- ► Leseverstärker zur Messung der Spannung auf der Bitline Schwellwertvergleich zur Entscheidung logisch 0/1

- Information muss anschließend neu geschrieben werden

- auch ohne Lese- oder Schreibzugriff ist regelmäßiger Refresh notwendig, wegen Selbstentladung (Millisekunden)

- 10  $\times$  langsamer als SRAM

- + DRAM für hohe Kapazität optimiert, minimaler Platzbedarf

- ▶ 6 Transistoren/bit

- statisch (kein refresh)

- schnell

- ▶ 1 Transistor/bit

- $ightharpoonup C = 5 \, \text{fF} \approx 47\,000 \, \text{Elektronen}$

- ► langsam (sense-amp)

64-040 Rechnerstrukturen und Betriebssysteme

11.4.1 Rechnerarchitektur I - Hardwarestruktur - Speicherbausteine

Abb. 7: Prototyp von Speicherzellen (Stapelkondensatoren) für zukünftige Speicherchips wie den Ein-Gigabi-Crip, Do für DraM-Chip eine minimale Speicherchagazität von 25 ffr notwendig ist, bringt es erhebliche Platzvortelle, die Kondensatorelemente vertikal übereinander zu stapeln. Die Diete der Schötelten betrött ein vas für um (Georgie Stemens).

# data-in wordline Masse bitline sense-amn data-out

IBM CMOS-6X embedded DRAM

#### Siemens 1 Gbit DRAM

- zwei Bauformen: "stacked" und "trench"

- Kondensatoren

- möglichst kleine Fläche

- ► Kapazität gerade ausreichend

- veraltete Varianten

- ► FPM: fast-page mode

- ► FDO: extended data-out

- heute gebräuchlich

- SDRAM: Ansteuerung synchron zu Taktsignal

- ▶ DDR-SDRAM: double-data rate Ansteuerung wie SDRAM Daten werden mit steigender und fallender Taktflanke übertragen

- ▶ DDR2 ... DDR5: Varianten mit höherer Taktrate aktuelle Übertragungsraten bis 51,2 GByte/sec pro Speicherkanal

- ► GDDR3...GDDR6X (Graphics DDR) derzeit bis 168 GByte/sec

- ► HBM . . . HBM3 (High Bandwidth Memory) derzeit bis 819,2 GByte/sec

- ► HMC...HMC2 (Hybrid Memory Cube) derzeit bis 480 GByte/sec

...DDR6 ×2

... GDDR7×1.5

# SDRAM: Lesezugriff auf sequenzielle Adressen

[Fur00]

Floating Gate

- ähnlich kompakt und kostengünstig wie DRAM

- ▶ nichtflüchtig (non-volatile): Information bleibt beim Ausschalten erhalten

- ▶ spezielle *floating-gate* Transistoren

- das floating-gate ist komplett nach außen isoliert

- einmal gespeicherte Elektronen sitzen dort fest

- Control Gate Oxidschicht

Source Drain

p

- Auslesen beliebig oft möglich, schnell

- Schreibzugriffe problematisch

- ▶ intern hohe Spannung erforderlich (Gate-Isolierung überwinden)

- ► Schreibzugriffe einer "0" nur blockweise

- ▶ pro Zelle nur einige 10 000 . . . 100 M Schreibzugriffe möglich

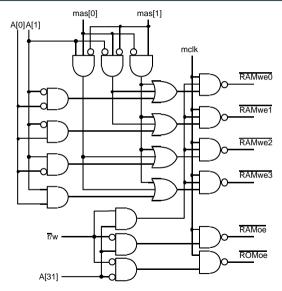

32-bit ARM Proz.  $4 \times 8$ -bit SRAMs  $4 \times 8$ -bit ROMs

[Fur00]

# Typisches Speichersystem: Adressdecodierung

11.4.1 Rechnerarchitektur I - Hardwarestruktur - Speicherbausteine

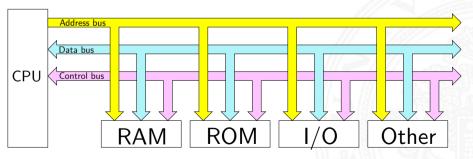

- ▶ **Bus:** elektrische (und logische) Verbindung

- mehrere Geräte

- mehrere Blöcke innerhalb einer Schaltung

- ▶ Bündel aus Daten- und Steuersignalen

- mehrere Quellen (und mehrere Senken [lesende Zugriffe])

- spezielle elektrische Realisierung:

Tri-State-Treiber oder Open-Drain

- ▶ Bus-Arbitrierung: wer darf, wann, wie lange senden?

- Master-Slave

- ▶ gleichberechtigte Knoten, Arbitrierungsprotokolle

- ▶ synchron: mit globalem Taktsignal vom "Master"-Knoten asynchron: Wechsel von Steuersignalen löst Ereignisse aus

- typische Aufgaben

- ► Kernkomponenten (CPU, Speicher . . . ) miteinander verbinden

- ▶ Verbindungen zu den Peripherie-Bausteinen

- ► Verbindungen zu Systemmonitor-Komponenten

- ▶ Verbindungen zwischen I/O-Controllern und -Geräten

**.** . . .

- ▶ viele Typen, standardisiert mit sehr unterschiedlichen Anforderungen

- ► High-Performance (= Datendurchsatz)

- einfaches Protokoll, billige Komponenten

- Multi-Master-Fähigkeit, zentrale oder dezentrale Arbitrierung

- ► Echtzeitfähigkeit, Daten-Streaming

- ▶ wenig Leitungen bis zu Zweidraht-Bussen: I<sup>2</sup>C, SPI, System-Management-Bus . . .

- ▶ lange Leitungen: EIA-485, RS-232, Ethernet . . .

- > Funkmedium: WLAN, Bluetooth

(logische Verbindung)

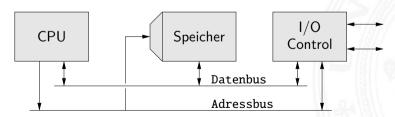

#### typisches *n*-bit Mikroprozessor-System:

- $\triangleright$  *n* Adress-Leitungen, also Adressraum  $2^n$  Bytes

- ▶ n Daten-Leitungen

- Adressbus

- **Datenbus**

Control

- Steuersignale

- clock: Taktsignal

- read/write: Lese-/Schreibzugriff (aus Sicht des Prozessors)

- ▶ wait: Wartezeit/-zyklen für langsame Geräte

- **>**

▶ um Leitungen zu sparen: teilweise gemeinsam genutzte Busse sowohl für Adressen als auch Daten ⇒ zusätzliches Steuersignal zur Auswahl Adressen/Daten

[TA14]

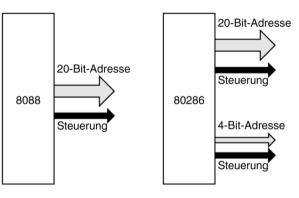

11.4.2 Rechnerarchitektur I - Hardwarestruktur - Busse

20-bit: 1 MiByte Adressraum

24-bit: 16 MiByte 32-bit: 4 GiByte

▶ alle Erweiterungen abwärtskompatibel

▶ 64-bit Architekturen: 48-, 56-, 64-bit Adressraum

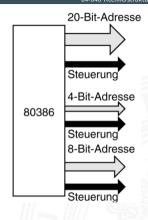

- alle Zeiten über Taktsignal Φ gesteuert

- ▶ *MREQ*-Signal zur Auswahl Speicher oder I/O-Geräte

- ▶ *RD* signalisiert Lesezugriff

- $\blacktriangleright$  Wartezyklen, solange der Speicher  $\overline{WAIT}$  aktiviert

#### ▶ typische Parameter

| Symbol [ns]                                                                                | ] Mir           | n Max |

|--------------------------------------------------------------------------------------------|-----------------|-------|

| $T_{AD}$ Adressausgabeverzögerung                                                          |                 | 4     |

| $T_{ML}$ Adresse ist vor $\overline{MREQ}$ stabil                                          | 2               |       |

| $T_M$ $\overline{MREQ}$ -Verzögerung nach fallender Flanke von $\Phi$ in $\overline{A}$    | $\mathcal{T}_1$ | 3     |

| $T_{RL}$ $RD$ -Verzögerung nach fallender Flanke von $\Phi$ in $T_1$                       |                 | 3     |

| $T_{DS}$ Setup-Zeit vor fallender Flanke von $\Phi$                                        | 2               |       |

| $T_{MH}$ $\overline{MREQ}$ -Verzögerung nach fallender Flanke von $\Phi$ in $\overline{A}$ | $T_3$           | 3     |

| $T_{RH}$ $\overline{RD}$ -Verzögerung nach fallender Flanke von $\Phi$ in $T_3$            |                 | 3     |

| $T_{DH}$ Hold-Zeit nach der Deaktivierung von $\overline{RD}$                              | 0               |       |

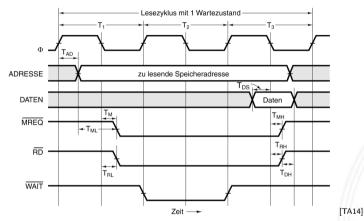

▶ Steuersignale  $\overline{MSYN}$ : Master fertig

SSYN: Slave fertig

▶ flexibler für Geräte mit stark unterschiedlichen Zugriffszeiten

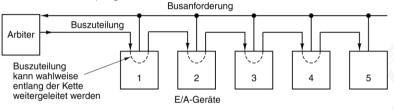

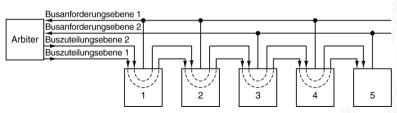

- ▶ mehrere Komponenten wollen Übertragung initiieren, aber nur ein Transfer zur Zeit

- der Bus Zugriff muss serialisiert werden

- 1. zentrale Arbitrierung

- ► Arbiter gewährt Bus-Requests

- Strategien

- Prioritäten für verschiedene Geräte

- "round-robin" Verfahren

- ..Token"-basierte Verfahren

- usw.

- 2. dezentrale Arbitrierung

- protokollbasiert

- Beispiel

- Komponenten sehen ob Bus frei ist

- wenn ja: Start der Übertragung; wenn nein: warten

- ▶ zur Kollisionserkennung: Daten vom Bus lesen

- ▶ bei Inkonsistenzen: Übertragung abbrechen und "später" erneut versuchen

- ► I/O-Geräte oft höher priorisiert als die CPU

- ▶ I/O-Zugriffe müssen schnell/sofort behandelt werden

- ► Benutzerprogramm kann warten

- ▶ Menge an (Nutz-) Daten, die pro Zeiteinheit übertragen werden kann

- ightharpoonup zusätzlicher Protokolloverhead  $\Rightarrow$  Brutto- / Netto-Datenrate

| RS-232          | 50 bit/sec              |     | 460 Kbit/sec                          |  |

|-----------------|-------------------------|-----|---------------------------------------|--|

| $I^2C$          | 100 Kbit/sec (Std       | .)  | 3,4 Mbit/sec (High Speed)             |  |

| USB             | 1,5  Mbit/sec  (1.x)    |     | 80 Gbit/sec (4.0v2)                   |  |

| ISA             | $128\mathrm{Mbit/sec}$  |     |                                       |  |

| PCI             | $1~{ m Gbit/sec}$ (2.0) | )   | 4,3 Gbit/sec (3.0)                    |  |

| AGP             | 2,1 Gbit/sec $(1x)$     |     | 34,1 Gbit/sec (8x 64-bit)             |  |

| PCI Express     | 2,0 Gbit/sec (1.x)      |     | $121~\text{Gbit/sec (7.0)}~\times 16$ |  |

| HyperTransport  | 25,6 Gbit/sec (1.0)     | ) ' | 409,6 Gbit/sec (3.1)                  |  |

| NVLink          | 640,0 Gbit/sec $(1.0)$  | )   | 1,8 Tbit/sec (4.0)                    |  |

| Infinity Fabric |                         |     | 4,1 Tbit/sec                          |  |

en.wikipedia.org/wiki/List\_of\_interface\_bit\_rates

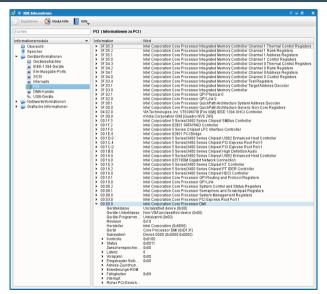

#### Peripheral Component Interconnect (Intel 1991)

- 33 MHz Takt

- ▶ 32-bit Bus-System

- gemeinsame Adress-/Datenleitungen

- Arbitrierung durch Bus-Master (die CPU)

- ► Abwärtskompatibilität

- ▶ PCI-Bus als logische Verbindung (SW-Layer) zu Komponenten

- ▶ technisch: PCle

- Auto-Konfiguration

- ▶ angeschlossene Geräte werden automatisch erkannt

- eindeutige Hersteller- und Geräte-Nummern

- ▶ Betriebssystem kann zugehörigen Treiber laden

- automatische Zuweisung von Adressbereichen und IRQs

optional 66 MHz Takt optional auch 64-bit

```

[maeder@tams165]~>lspci -v

00:00.0 Host bridge: Intel Corporation Sky Lake Host Bridge/DRAM Registers (rev 08)

Subsystem: Dell Device 06dc

Flags: bus master, fast devsel, latency 0

Capabilities: <access denied>

00:02.0 VGA compatible controller: Intel Corporation Sky Lake Integrated Graphics (rev 07)

Subsystem: Dell Device 06dc

Flags: bus master, fast devsel, latency 0, IRQ 134

Memory at e0000000 (64-bit, non-prefetchable) [size=16M]

Memory at d0000000 (64-bit, prefetchable) [size=256M]

I/O ports at f000 [size=64]

Expansion ROM at <unassigned> [disabled]

Capabilities: <access denied>

Kernel driver in use: i915 bpo

00:04.0 Signal processing controller: Intel Corporation Device 1903 (rev 08)

Subsystem: Dell Device O6dc

Flags: bus master, fast devsel, latency 0, IRO 16

Memory at e1340000 (64-bit, non-prefetchable) [size=32K]

Canabilities: <access denied>

Kernel driver in use: proc_thermal

00:14.0 USB controller: Intel Corporation Device 9d2f (rev 21) (prog-if 30 [XHCI])

Subsystem: Dell Device 06dc

Flags: bus master, medium devsel, latency 0, IRO 125

Memory at e1330000 (64-bit, non-prefetchable) [size=64K]

```

## PCI-Bus: Peripheriegeräte (cont.)

11.4.2 Rechnerarchitektur I - Hardwarestruktur - Busse

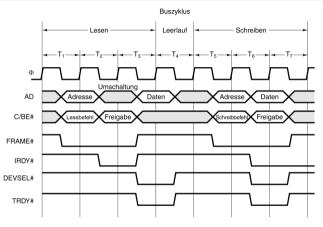

| Signal  | Leitungen | Master | Slave | Beschreibung                                              |

|---------|-----------|--------|-------|-----------------------------------------------------------|

| CLK     | 1         |        |       | Takt (33 oder 66 MHz)                                     |

| AD      | 32        | ×      | ×     | Gemultiplexte Adress- und Datenleitungen                  |

| PAR     | 1         | ×      |       | Adress- oder Datenparitätsbit                             |

| C/BE    | 4         | ×      |       | Busbefehl/Bitmap für Byte Enable                          |

|         |           |        |       | (zeigt gültige Datenbytes an)                             |

| FRAME#  | 1         | ×      |       | Kennzeichnet, dass AD und C/BE aktiviert sind             |

| IRDY#   | 1         | ×      |       | Lesen: Master wird akzeptieren                            |

|         |           |        |       | Schreiben: Daten liegen an                                |

| IDSEL   | 1         | ×      |       | Wählt Konfigurationsraum statt Speicher                   |

| DEVSEL# | 1         |        | ×     | Slave hat seine Adresse decodiert und ist in Bereitschaft |

| TRDY#   | 1         |        | ×     | Lesen: Daten liegen an                                    |

|         |           |        |       | Schreiben: Slave wird akzeptieren                         |

| STOP#   | 1         |        | ×     | Slave möchte Transaktion sofort abbrechen                 |

| PERR#   | 1         |        |       | Empfänger hat Datenparitätsfehler erkannt                 |

| SERR#   | 1         |        |       | Adressparätätsfehler oder Systemfehler erkannt            |

| REQ#    | 1         |        |       | Bus-Arbitration: Anforderung des Busses                   |

| GNT#    | 1         |        |       | –"– Zuteilung des Busses                                  |

| RST#    | 1         |        |       | Setzt das System und alle Geräte zurück                   |

[TA14]

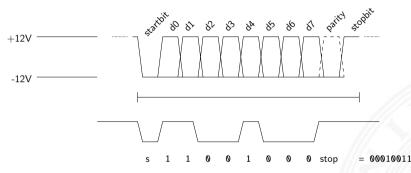

- ► Baudrate 300, 600, . . . , 19 200, 38 400, 115 200 bits/sec

- Anzahl Datenbits 5, 6, 7, 8

Anzahl Stopbits 1, 2

Parität none, odd, even

- ▶ minimal drei Leitungen: GND, TX, RX (Masse, Transmit, Receive)

- ▶ oft weitere Leitungen für erweitertes Handshake

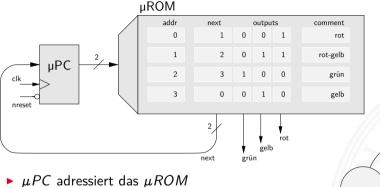

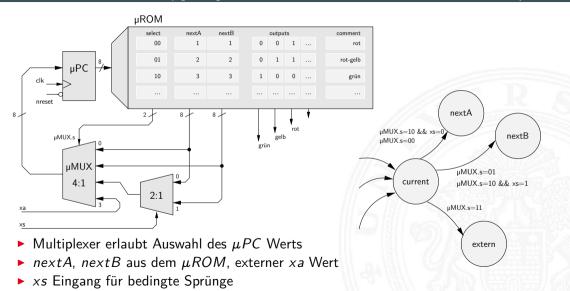

- ▶ als Alternative zu direkt entworfenen Schaltwerken

- Mikroprogrammzähler μPC: Register für aktuellen Zustand

- $\blacktriangleright \mu PC$  adressiert den Mikroprogrammspeicher  $\mu ROM$

- ightharpoonup  $\mu ROM$  konzeptionell in mehrere Felder eingeteilt

- ▶ die verschiedenen Steuerleitungen

- ein oder mehrere Felder für Folgezustand

- ▶ ggf. zusätzliche Logik und Multiplexer zur Auswahl unter mehreren Folgezuständen

- ▶ ggf. Verschachtelung und Aufruf von Unterprogrammen: "nanoProgramm"

- ▶ siehe "Praktikum Rechnerstrukturen und Betriebssysteme"

- next-Ausgang liefert Folgezustand

- andere Ausgänge steuern die Schaltung = die Lampen der Ampel

### Mikroprogramm: Beispiel zur Auswahl des Folgezustands

11.4.3 Rechnerarchitektur I - Hardwarestruktur - Mikroprogrammierung

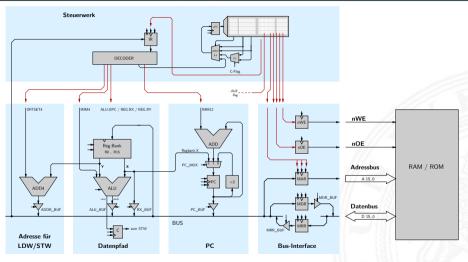

#### Praktikum RSB: D-CORE

11.4.3 Rechnerarchitektur I - Hardwarestruktur - Mikroprogrammierung

- ▶ aktuelle Architekturen: weniger Mikroprogrammierung

- ⇒ Pipelining (folgt in 14 Rechnerarchitektur II − Pipelining)

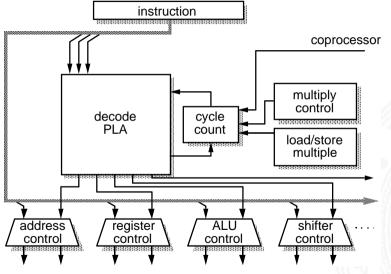

### Mikroprogramm: Befehlsdecoder des ARM 7 Prozessors

11.4.3 Rechnerarchitektur I - Hardwarestruktur - Mikroprogrammierung

64-040 Rechnerstrukturen und Betriebssysteme

controller timer

test i/f ctrl

external bus interface

**UART**

parallel i/f

S. Furber: ARM System-on-Chip Architecture [Fur00]

11.4.4 Rechnerarchitektur I - Hardwarestruktur - Beispielsystem: ARM

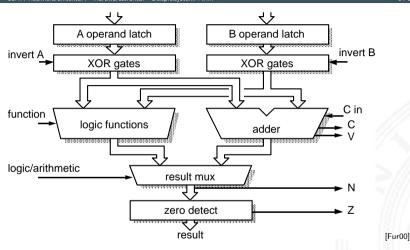

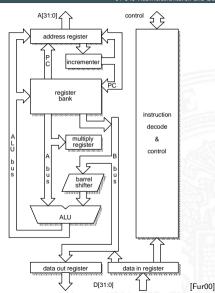

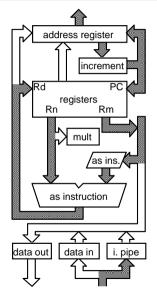

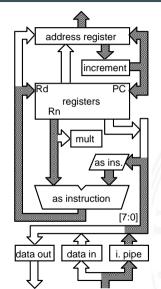

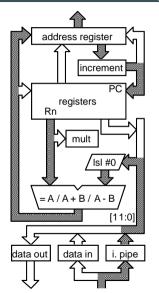

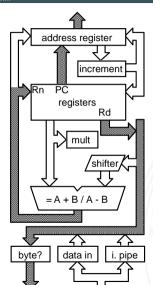

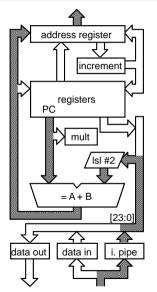

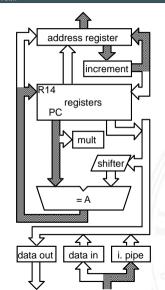

▶ Register für die Operanden A und B

► Addierer und separater Block für logische Operationen

[Fur00]

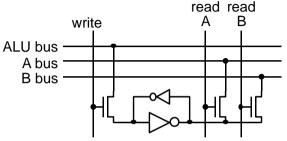

- ▶ Prinzip wie 6T-SRAM: rückgekoppelte Inverter

- ▶ mehrere (hier zwei) parallele Lese-Ports

- ▶ mehrere Schreib-Ports möglich, aber kompliziert

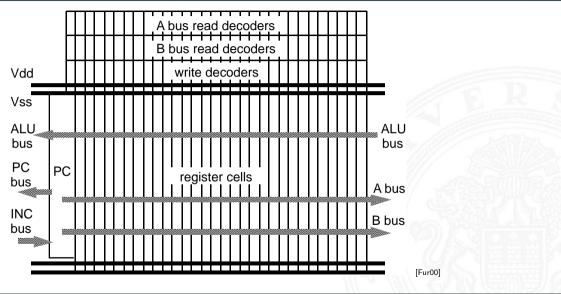

# Multi-Port Registerbank: Floorplan/Chiplayout

11.4.4 Rechnerarchitektur I - Hardwarestruktur - Beispielsystem: ARM

- Registerbank (inkl. Program Counter)

- ► Inkrementer

- ► Adress-Register

- ► ALU, Multiplizierer, Shifter

- Speicherinterface (Data-In / -Out)

- Steuerwerk

- ▶ bis ARM 7: 3-stufige Pipeline *fetch, decode, execute*

### ARM Datentransfer: Register-Operationen

11.4.4 Rechnerarchitektur I - Hardwarestruktur - Beispielsystem: ARM

# ARM Datentransfer: Funktionsaufruf/Sprungbefehl

11.4.4 Rechnerarchitektur I - Hardwarestruktur - Beispielsystem: ARM

- "Choreografie" der Funktionseinheiten

- ▶ Wie wird ein Programm gestartet?

- Was passiert beim Einschalten des Rechners?

- Erweiterungen des von-Neumann Konzepts

- parallele, statt sequenzieller Befehlsabarbeitung

- $\Rightarrow$  Pipelining

- mehrere Ausführungseinheiten

- ⇒ superskalare Prozessoren, Mehrkern-Architekturen

- dynamisch veränderte Abarbeitungsreihenfolge

- $\Rightarrow$  "out-of-order execution"

- getrennte Daten- und Instruktionsspeicher

- ⇒ Harvard-Architektur

- ► Speicherhierarchie, Caches etc.

- → siehe Kapitel 14 Rechnerarchitektur II

### Hardwareorganisation eines typischen Systems

11.5 Rechnerarchitektur I - Wie rechnet ein Rechner?

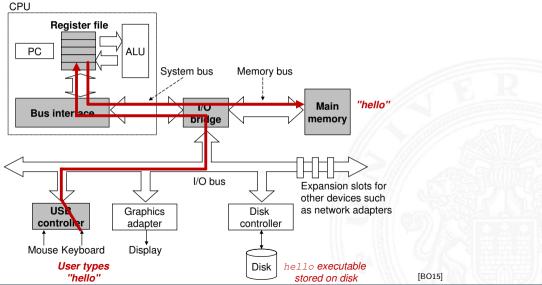

# Programmausführung: 1. Benutzereingabe

11.5 Rechnerarchitektur I - Wie rechnet ein Rechner?

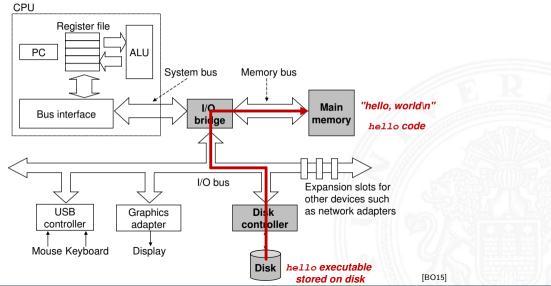

### Programmausführung: 2. Programm laden

11.5 Rechnerarchitektur I - Wie rechnet ein Rechner?

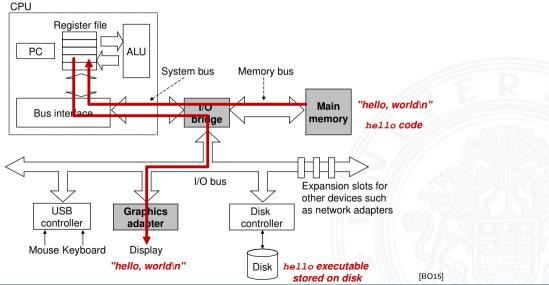

# Programmausführung: 3. Programmlauf

11.5 Rechnerarchitektur I - Wie rechnet ein Rechner?

- ► Chipsatz erzeugt Reset-Signale für alle ICs

- ▶ Reset für die zentralen Prozessor-Register (PC . . . )

- ▶ PC wird auf Startwert initialisiert

- ► Befehlszyklus wird gestartet

- ▶ Initialisierung und Selbsttest des Prozessors

- ▶ Interrupt (APIC) / Protokoll getrieben: Auswahl des Bootstrap Kerns

- ▶ Prozessor greift auf Startadresse zu, wo Boot-Programm beginnt (ROM, Flash)

- Löschen und Initialisieren der Caches

- Konfiguration des Chipsatzes

- ► Erkennung und Initialisierung von I/O-Komponenten

- ▶ Laden des Betriebssystems, dabei Start aller CPU-Kerne

#### 11.6 Rechnerarchitektur I - Literatur

#### [BO15] R.E. Bryant, D.R. O'Hallaron:

Computer systems – A programmers perspective. 3rd global ed., Pearson Education Ltd., 2015.

ISBN 978-1-292-10176-7

[TA14] A.S. Tanenbaum, T. Austin:

csapp.cs.cmu.edu

Rechnerarchitektur – Von der digitalen Logik zum Parallelrechner.

6. Auflage, Pearson Deutschland GmbH, 2014.

ISBN 978-3-8689-4238-5

[Fur00] S. Furber: ARM System-on-Chip Architecture.

2nd edition, Pearson Education Limited, 2000.

ISBN 978-0-201-67519-1

[GK83] D.D. Gajski, R.H. Kuhn: Guest Editors' Introduction: New VLSI Tools.

in: IEEE Computer 16 (1983), December, Nr. 12, S. 11–14.

ISSN 0018-9162

#### 11.6 Rechnerarchitektur I - Literatur

- [PH22] D.A. Patterson, J.L. Hennessy: Rechnerorganisation und Rechnerentwurf Die Hardware/Software-Schnittstelle MIPS Edition.

- 6. Auflage, De Gruyter Oldenbourg, 2022.

ISBN 978-3-11-075598-5

- [PH20] D.A. Patterson, J.L. Hennessy: Computer Organization and Design –

The Hardware Software Interface RISC-V Edition.

2nd edition, Morgan Kaufmann Publishers Inc., 2020. ISBN 978-0-12-820331-6

- [Mäd11] A. Mäder: Vorlesung: Rechnerarchitektur und Mikrosystemtechnik. Universität Hamburg, FB Informatik, 2011, Vorlesungsfolien. tams.informatik.uni-hamburg.de/lectures/2011ws/vorlesung/ram

- [HenHA] N. Hendrich: HADES HAmburg DEsign System.

Universität Hamburg, FB Informatik, Lehrmaterial.

tams.informatik.uni-hamburg.de/applets/hades/webdemos