Vorlesung: Rechnerstrukturen, Teil 2 (Modul IP7)

# Vorlesung: Rechnerstrukturen, Teil 2 (Modul IP7)

#### J. Zhang

zhang@informatik.uni-hamburg.de

Universität Hamburg Fachbereich Informatik

AB Technische Aspekte Multimodaler Systeme

10. Januar 2003

10. Januar 2003

| Wie rechnet ein Rechner? | Rechnerstrukturen | Beschreibungsebenen | Motivation | "Moore's Law" | 2. Einführung in die Rechnerarchitektur | 1. Allgemeine Informationen . | Inhaltsverzeichnis | T A Arbeitsbereich TAMS MIS Fachbereich Informatik |

|--------------------------|-------------------|---------------------|------------|---------------|-----------------------------------------|-------------------------------|--------------------|----------------------------------------------------|

|                          |                   |                     |            |               | nitel                                   |                               |                    |                                                    |

|                          |                   |                     |            |               | tur                                     |                               |                    |                                                    |

|                          |                   |                     |            |               |                                         |                               |                    |                                                    |

|                          |                   |                     |            |               |                                         |                               |                    | <b>≤</b>                                           |

|                          |                   |                     |            |               |                                         |                               |                    | les                                                |

| ٠                        | •                 | •                   | •          | •             | •                                       | •                             |                    |                                                    |

| :                        |                   |                     |            |               |                                         |                               |                    | 굕                                                  |

|                          |                   |                     |            |               |                                         |                               |                    | chne                                               |

| :                        | :                 | :                   | :          | :             | :                                       | :                             |                    | ersti                                              |

|                          |                   |                     |            |               |                                         |                               |                    | ř.                                                 |

| ٠                        | ٠                 |                     |            |               |                                         | ٠                             |                    | ure                                                |

| :                        |                   |                     |            |               |                                         |                               |                    | ,<br>-                                             |

|                          |                   |                     |            |               |                                         |                               |                    | ⊕:                                                 |

| 31                       | 22                | 12                  | 9          | 6             | 4                                       | ω                             |                    | €                                                  |

|                          |                   |                     |            |               |                                         |                               |                    | Vorlesung: Rechnerstrukturen, Teil 2 (Modul IP7)   |

10. Januar 2003

Kapitel: Allgemeine Informationen

### Allgemeine Informationen

Vorlesung (1): Di. u. Do. 10:00 c.t - 11:00 Pause: 11:00 - 11:10

Vorlesung (2):

11:10 - 11:55

Raum: Web:

http://tams-www.informatik.uni-hamburg.de/lehre/

Prof. Dr. Jianwei Zhang

E-mail: Büro: Sprechstunde:

Name:

zhang@informatik.uni-hamburg.de Donnerstag 15:00 - 16:00 Tatjana Tetsis

Büro: Sekretariat:

E-mail: tetsis@informatik.uni-hamburg.de

Seite 3 10. Januar 2003

Kapitel: Einführung in die Rechnerarchitektur

## Einführung in die Rechnerarchitektur

Rapide sich veränderndes Gebiet:

- Vakuum Röhre Transistor IC VLSI

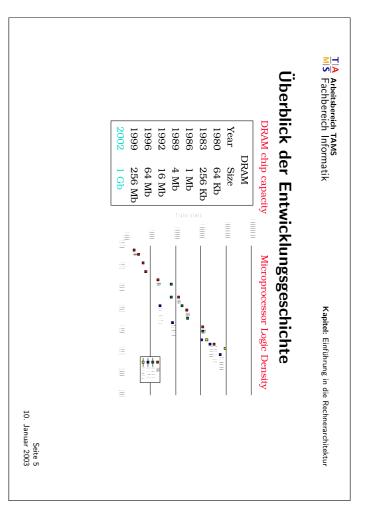

- verdoppelt sich alle 1,5 Jahre ("Moore's Law"):

- Speicherkapazität

- Prozssorgeschwindigkeit (durch Fortschritt in der Technologie und der Organisation)

Seite 4 10. Januar 2003

Kapitel: Einführung in die Rechnerarchitektur

Abschnitt: "Moore's Law"

### "Moore's Law"

Umgangssprachliche Formulierung:

Bei konstanten Kosten verdoppelt sich die Rechenleistung eines Mikroprozessors alle 18 Monate.

Bemerkungen:

- Moores Vermutung bestätigt sich seit 1975.

- Moores ursprüngliche Aussage betrifft die Steigerungsrate für die Anzahl der Schaltkreise auf einem Chip.

- Moores Vermutung wird allgemein als "Moore's Law" bezeichnet.

Seite 6 10. Januar 2003

Kapitel: Einführung in die Rechnerarchitektur Abschnitt: "Moore's Law"

### "Moore's Law" - Formel

$L(t) = L(0) \times 2^{t/18}$

Die Zeit t wird in Monaten gemessen.

L(t) = Leistung zum Zeitpunkt t.

L(0) = Leistung zum Zeitpunkt 0.

Einige Formelwerte:

Jahr 1: Jahr 2: Jahr 3: Jahr 5: Jahr 6: Jahr 7: Jahr 8: 1,5874 2,51984

10,0794

16 25,3984 40,3175

Seite 7 10. Januar 2003

TIA Arbeitsbereich TAMS

MIS Fachbereich Informatik

Kapitel: Einführung in die Rechnerarchitektur Abschnitt: "Moore's Law"

# Leistungssteigerung der Spitzenrechner seit 1993

| 5.104       | 35.610          | Earth Simulator, NEC                 | 2002 |

|-------------|-----------------|--------------------------------------|------|

| 7.424       | 7.226           | ASCI White, IBM (SP Power 3)         | 2001 |

| 7.424       | 4.903           | ASCI White, IBM (SP Power 3)         | 2000 |

| 9.632       | 2.379           | ASCI Intel Red (Pentium II Xeon)     | 1999 |

| 5.808       | 2.144           | ASCI Blue-Pacific (IBM SP 640E)      | 1998 |

| 9.152       | 1.338           | Intel ASCI Red (200 MHz Pentium Pro) | 1997 |

| 2.048       | 368             | Hitachi CP-PACS                      | 1996 |

| 6.768       | 281             | Intel Paragon XP/S MP                | 1995 |

| 6.768       | 281             | Intel Paragon XP/S MP                | 1994 |

| 140         | 124             | Fujitsu NWT                          | 1993 |

| Prozessoren | in Gflop/s      |                                      |      |

| Zahl der    | Linpackleistung | Rechner                              | Jahr |

Seite 8 10. Januar 2003

Kapitel: Einführung in die Rechnerarchitektur

Abschnitt: Motivation

#### Motivation

Was Sie lernen werden:

- wie Computer funktionieren, als grundlegende Basis

- wie man ihre Leistung analysiert (und wie nicht)

- Fragen moderner Prozessoren (Caches, Pipelines)

Warum sollte man diese Dinge lernen?

- Sie wollen Computerwissenschaftler werden

- Sie wollen Software entwickeln, die praktisch genutzt wird (daher brauchen wir Leistung)

- Hardware wird immer enger mit Software als Embedded Systems gekoppelt

- Sie müssen Verkaufsentscheidungen treffen oder einen "Expertenrat" abgeben

Seite 9 10. Januar 2003

Kapitel: Einführung in die Rechnerarchitektur Abschnitt: Motivation

## Bereiche der Technischen Informatik

Mechatronik, Robotik, Echtzeit-Regelung, Prozeßrechentechnik, Embedded-Systems. Der Rest liegt in Anwendungsfeldern der Mikroelektronik.

Seite 10 10. Januar 2003

Kapitel: Einführung in die Rechnerarchitektur

Abschnitt: Motivation

### Motivation - 2

Was zieht uns an:

- Veränderung

- Es ist aufregend

- Es wird noch aufregender

- Große Bedeutung für alle anderen Aspekte der E-Technik und Informatik

Seite 11 10. Januar 2003

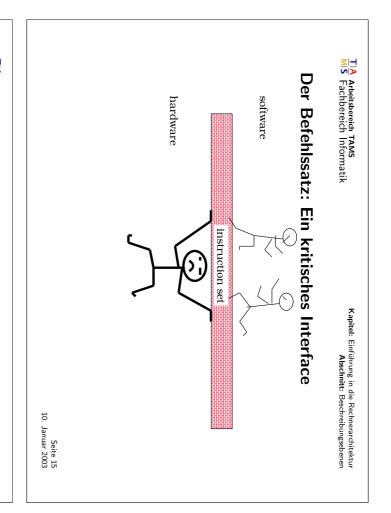

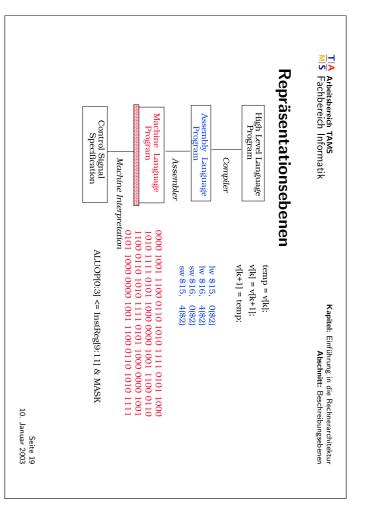

Kapitel: Einführung in die Rechnerarchitektur Abschnitt: Beschreibungsebenen

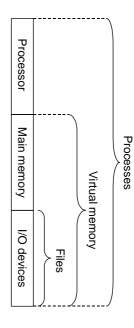

# Beschreibungsebenen - eine Schichten-Ansicht

| - Hardware | 7             | I/O devices | Main memory          | Processor |

|------------|---------------|-------------|----------------------|-----------|

|            |               |             | Operating system     |           |

| Software   | $\overline{}$ | is          | Application programs |           |

Kapitel: Einführung in die Rechnerarchitektur

Abschnitt: Beschreibungsebenen

# Von einem Betriebssystem gelieferte Abstraktionen

Seite 13 10. Januar 2003

TIA Arbeitsbereich TAMS MIS Fachbereich Informatik

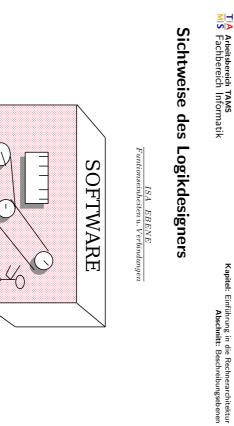

Kapitel: Einführung in die Rechnerarchitektur Abschnitt: Beschreibungsebenen

Befehlssatzarchitektur: Instruction Set Architecture (ISA): die vom Programmierer betrachteten Attribute der konzeptionellen Struktur

Befehlssatzarchitektur (ISA)

+ des funktionellen Verhaltens, die beinhalten:

- Organisation des programmierbaren Speichers

- Datentypen und Datenstrukturen: Codierungen und Darstellungen

- Befehlssatz

- Befehlsformate

- Modelle für Befehls- und Datenzugriffe

- Ausnahmebedingungen

Seite 14 10. Januar 2003

Seite 16 10. Januar 2003

Kapitel: Einführung in die Rechnerarchitektur Abschnitt: Beschreibungsebenen

## Beispiele für Befehlssatzarchitekturen

Seite 17 10. Januar 2003

Kapitel: Einführung in die Rechnerarchitektur Abschnitt: Beschreibungsebenen

### Das Kompilierungssystem

Seite 18 10. Januar 2003

Kapitel: Einführung in die Rechnerarchitektur

Abschnitt: Beschreibungsebenen

#### **Assembler**

In Assembler werden Sie selten ein Programm schreiben müssen.

### Verständnis des Ausführungsmodells auf der Maschinenebene: Das Verständnis des Assemblers ist unerlässlich für das

- Programmverhalten bei Fehlern

- Das High-Level Sprachmodell ist dort nicht anwendbar

- Die Programmleistung verstärken

- Die Ursachen für Programm-Ineffizienz verstehen

- Systemsoftware implementieren

- Der Compiler hat den Maschinencode als Ziel

- Die Betriebssysteme müssen den Prozesszustand verwalten

Seite 20 10. Januar 2003

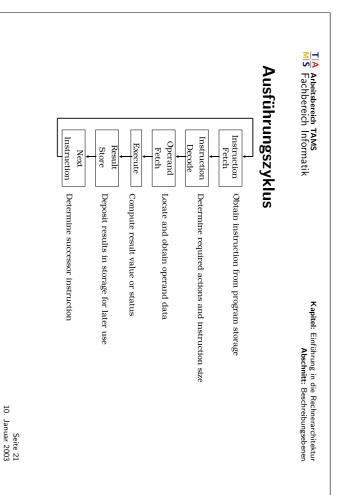

### Rechnerstrukturen

Bestandteile eines Rechners:

- Input (Maus, Keyboard)

- Output (Bildschirm, Drucker)

- Speicher (Laufwerke, DRAM, SRAM, CD)

- Netzwerk

Unser primärer Schwerpunkt: der Prozessor (Datenpfad und Kontrolle)

- wird mit Hilfe von Millionen Transistoren implementiert

- ist unmöglich durch die Untersuchung jedes einzelnen Transistors zu verstehen

- Wir brauchen...

Seite 22 10. Januar 2003

## Rechnerstrukturen - Weitere Betrachtung

Rechnerstrukturen =

- Rechnerarchitektur

- Implementierung

Rechnerarchitektur =

- Schnittstelle zwischen Rechner und Benutzer =

- Befehlssatzarchitektur

- Maschinenorganisation

Implementierung

- Hardware-Aufbau von Komponenten, die die Rechnerarchitektur realisieren

- Speichereinheiten, Recheneinheiten, Verbindungssysteme,...

Seite 23 10. Januar 2003

Kapitel: Einführung in die Rechnerarchitektur

Abschnitt: Rechnerstrukturen

# Was umfasst der Begriff Rechnerstrukturen?

Rechnerstrukturen

- Koordination vieler Abstraktionsebenen der Beschreibung

- Berücksichtigung ständig wechselnder äußerer Einflüsse

- Entwurf, Leistungsmessung, Leistungsbewertung

Seite 24 10. Januar 2003

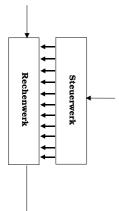

### Maschinenorganisation

- Fähigkeiten und Leistung der prinzipiellen Funktionseinheiten

- ♦ (z.B., Registers, ALU, Shifters,...)

- Verbindungen zwischen diesen Einheiten

- Informationsfluss zwischen den Komponenten

- Logik und Methoden zur Realisierung des Informationsflusses

- "Choreographie" der Funktionseinheiten

- Beschreibung auf Register-Transfer-Ebene (Register Transfer Level (RTL))

Seite 25 10. Januar 2003

Kapitel: Einführung in die Rechnerarchitektur

Abschnitt: Rechnerstrukturen

### von Neumann Architektur

Charakteristika:

- 1. Daten und Befehle liegen im gleichen Schreib-Lese-Speicher.

- Der Zugriff auf Speicherinhalte erfolgt über die Adresse der Speicherzelle, Speicherinhalte sind nicht typisiert.

- 3. Die Programmausführung erfolgt sequentiell, Befehl für Befehl.

Seite 26 10. Januar 2003

## Treibende Kräfte auf Rechnerstrukturen

- Technologie

- Anwendungen

- Programmiersprachen

- Betriebssysteme

- Geschichte

Seite 27 10. Januar 2003

TIA Arbeitsbereich TAMS

MIS Fachbereich Informatik

Kapitel: Einführung in die Rechnerarchitektur

Abschnitt: Rechnerstrukturen

### Technologie

- Gegen 1985 enstehen Ein-Chip 32-Bit Prozessoren und Single-Board-Computer

- Workstations, PCs, Multiprozessoren basieren seither auf dieser Technik

- Mit den neu auf dem Markt erscheinenden Prozessoren ist Mainframe-Leistung auf einem Chip verfügbar

Seite 28 10. Januar 2003

# Technologiebedingtes Wachstum in Zahlen

- Prozessor

- ♦ Transistorzahl: ca 30% pro Jahr (heute ca. 100 Mio.)

- ♦ Taktrate: ca 20 % pro Jahr

- Speicher

- ♦ DRAM Kapazität: ca 60% pro Jahr (4x alle 3 Jahre)

- ◆ Zugriffsgeschwindigkeit: ca. 10 % pro Jahr

- ♦ Kosten pro Bit: sinken um ca. 25% pro Jahr

- Plattenspeicher

- ♦ Kapazitätssteigerung: ca. 60% pro Jahr

Seite 29 10. Januar 2003

Kapitel: Einführung in die Rechnerarchitektur

Abschnitt: Rechnerstrukturen

## Beispiel: Der PowerPC 7540 (G4)

$U_{int}$ Leistung  $U_{I/O}$ Bus Interface Busfrequenz Geschwindigkeit bis 1,2 GHZ L1 Cache Performance Prozess L2 Cache 1,8V / 2,5 V 21,3 W / 1 GHz 64 Bits 32/32 kByte  $0,18~\mu\mathrm{m}$ MPS @ 1GHz 2280 Drystone 1,3 - 1,6V 256 kByte 133 MHz

Seite 30 10. Januar 2003

Kapitel: Einführung in die Rechnerarchitektur Abschnitt: Wie rechnet ein Rechner?

### Wie rechnet ein Rechner?

- Datenpfad und Steuerwerk

- Choreografie der Funktionseinheiten

- Caches und Speicherhierarchien

- Wie man Daten sicher verwahrt

Ein-/Ausgabe und Netzwerke

- "Hello World" Wie man mit Rechnern kommuniziert

Seite 31 10. Januar 2003

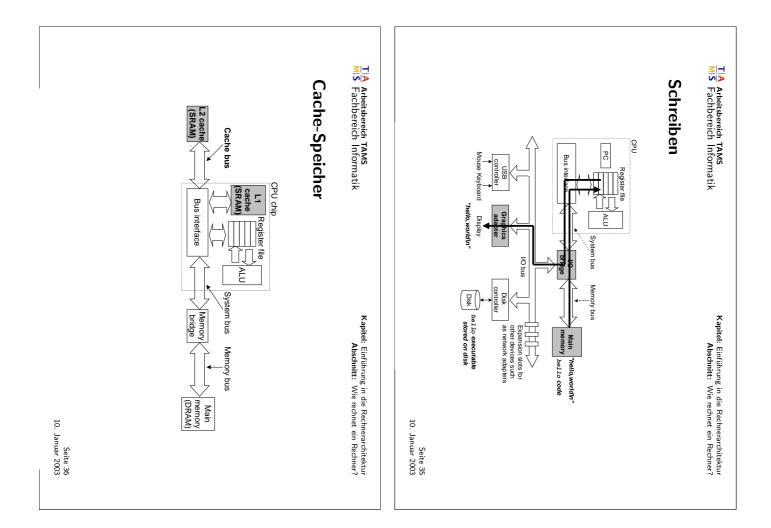

Kapitel: Einführung in die Rechnerarchitektur Abschnitt: Wie rechnet ein Rechner?

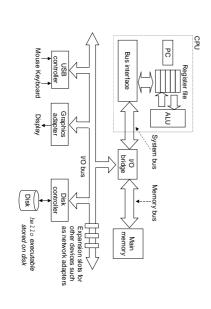

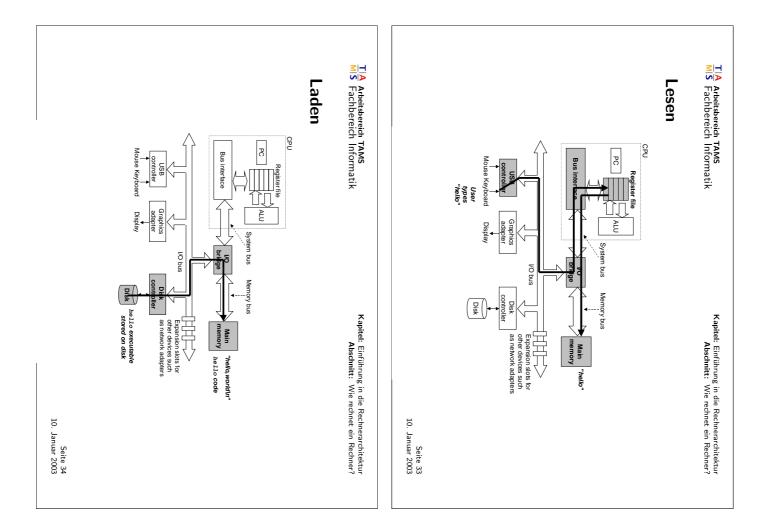

# Hardwareorganisation eines typischen Systems

Seite 32 10. Januar 2003

Kapitel: Einführung in die Rechnerarchitektur Abschnitt: Wie rechnet ein Rechner?

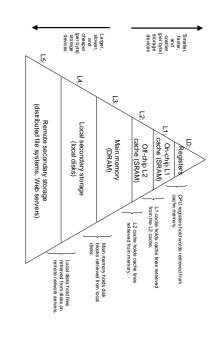

## Beispiel einer Speicher-Hierarchie

Seite 37 10. Januar 2003

TIA Arbeitsbereich TAMS

MIS Fachbereich Informatik

Kapitel: Einführung in die Rechnerarchitektur Abschnitt: Wie rechnet ein Rechner?

### Der Speicher ist wichtig

- Der Speicher ist nicht unbegrenzt

- Er muss zugeteilt und verwaltet werden.

- ♦ Viele Anwendungen werden vom Speicher dominiert.

- Fehler, die auf den Speicher verweisen, sind besonders gefährlich

- Auswirkungen sind sowohl zeitlich als auch räumlich entfernt

- Speicherleistung ist nicht gleichbleibend

- ♦ Cache und Virtual Memory Auswirkungen können die Programmleistung stark beeinflussen

- ♦ Die Anpassung des Programms an das Speichersystem kann die Geschwindigkeit bedeutend verbessern

Seite 38 10. Januar 2003

Kapitel: Einführung in die Rechnerarchitektur Abschnitt: Wie rechnet ein Rechner?

### Ergänzende Literatur

Zur Rechnerarchitektur (1. Teil)

#### Literatur

- [1] Randal E. Bryant and David O'Hallaron. *Computer Systems*. Pearson Education, Inc., New Jersey, 2003.

- [2] David A. Patterson and John L. Hennessy. Computer Organization and Design. The Hardware / Software Interface. Morgan Kaufmann Publishers, Inc., San Francisco, 1998.

- [3] Andrew S. Tanenbaum. *Computerarchitektur*. Pearson Studium München, 2006.

Seite 39 10. Januar 2003