| WS 2004/05 | Übungen                      | Aufgabenblatt 5 |

|------------|------------------------------|-----------------|

|            | Technische Informatik 1 (T1) |                 |

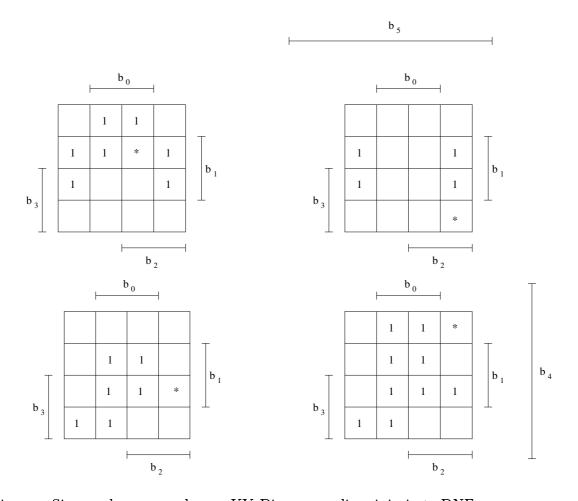

Aufgabe 5.1 Minimierung (4 Punkte)

Bestimmen Sie aus dem angegebenen KV-Diagramm die minimierte DNF.

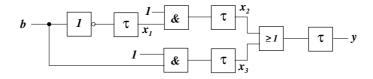

## Aufgabe 5.2 Hazards (4 Punkte)

Untersuchen Sie die folgende Schaltung auf Hazards:

$$b \xrightarrow{I} x_1 & x_2 \\ \downarrow I & \downarrow x_3 \\ \downarrow I & \downarrow X_4 \\ \downarrow I & \downarrow X_3 \\ \downarrow I & \downarrow X_4 \\ \downarrow I & \downarrow X_4 \\ \downarrow I & \downarrow X_5 \\ \downarrow I & \downarrow X$$

Nehmen Sie an, dass alle Gatter die gleiche Signallaufzeit  $\tau$  haben und keine Laufzeiten auf den Verbindungsleitungen vorhanden sind:

- a) Tragen Sie die Signallaufzeiten in die Schaltfunktion  $y(t) = b(t ...) \vee \overline{b}(t ...)$  ein.

- b) Zeichnen Sie in das vorgegebene Impulsdiagramm die Signalverläufe für die Ausgänge  $x_1$  bis  $x_4$  und y ein, wenn am Eingang b einRechteckimpuls der Dauer  $4\tau$  angelegt wird.

c) Klassifizieren Sie den Hazard, der am Ausgang y entsteht.

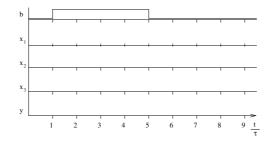

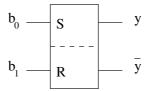

# Aufgabe 5.3 RS-Flipflop (2 Punkte)

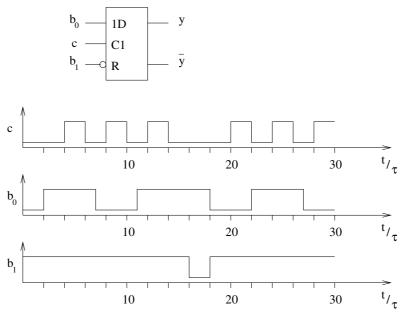

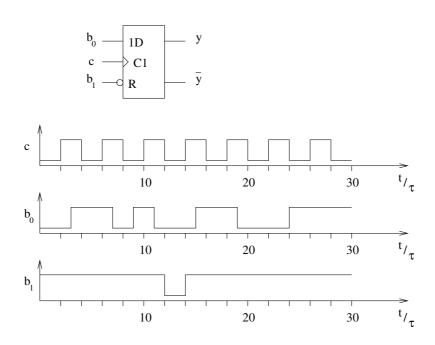

a) Gegeben ist ein RS-Flipflop:

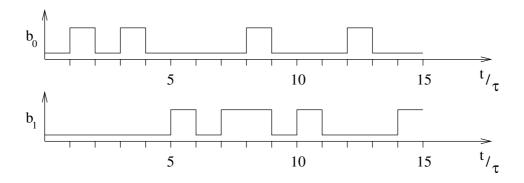

Die Eingangssignale  $b_0$  und  $b_1$  haben den folgenden Zeitverlauf:

Geben Sie das Impulsdiagramm für die Ausgangssignale y und  $\overline{y}$  an; für  $t/\tau=0$  sei das Flipflop zurückgesetzt.

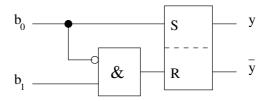

**b)** Der R-Eingang des RS-Flipflops wird wie folgt beschaltet:

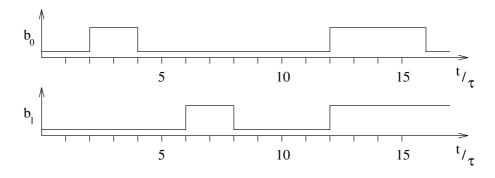

Die Eingangssignale haben nun den folgenden Verlauf:

Geben Sie wiederum den Zeitverlauf der Ausgangssignale an; der Anfangszustand entspricht dem in a).

c) Worin unterscheiden sich die Schaltungen in a) und b)?

# Aufgabe 5.4 JK-Flipflop (2 Punkte)

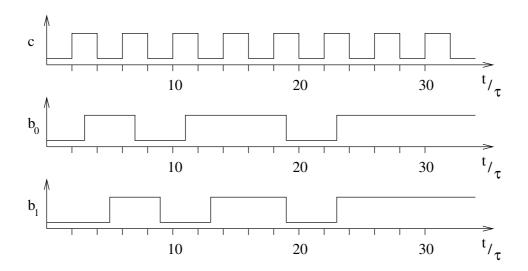

Gegeben ist ein einflankengesteuertes JK-Flipflop, welches bei der abfallenden Taktflanke schaltet:

Bestimmen Sie den Verlauf der Ausgangssignale bei dem gegebenen Impulsdiagramm für die Eingangssignale; das Flipflop sei zu Beginn zurückgesetzt. Die Setz- und Haltezeiten werden in allen Ausgabenpunkten eingehalten.

## Aufgabe 5.5 D-Flipflop (2 Punkte)

a) Gegeben ist ein taktzustandsgesteuertes D-Flipflop mit dem angegebenen Verlauf der Eingangssignale. Ergänzen Sie das Impulsdiagramm um die Ausgangssignale, wenn zu Beginn das Flipflop zurückgesetzt ist.

b) Betrachten Sie nun ein einflankengesteuertes D-Flipflop. Bestimmen Sie wiederum die Zeitverläufe an den Ausgängen, wobei Sie annehmen können, dass die Setz- und Haltezeiten berücksichtigt werden.

### Aufgabe 5.6 4-Bit Binärzähler (6 Punkte)

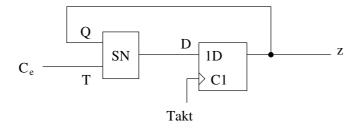

Entwickeln Sie einen synchronen 4-Bit Binärzähler mit D-Flipflops. Bezeichnen Sie die Zustandsvariablen mit  $(z_3z_2z_1z_0)$ . Sehen Sie einen Eingang 'Counter Enable' und einen Ausgang zur Anzeige des Überlaufs vor.

Das D-Flipflop ist durch folgende Übergangstabelle spezifiziert:

$$\begin{array}{c|c} D & Q_{n+1} \\ \hline 0 & 0 \\ 1 & 1 \end{array}$$

Mit einem D-Flipflop und einem Schaltnetz (SN) vor dem D-Eingang

lässt sich ein 1-Bit-Zähler mit einem Eingang 'Counter Enable'  $(C_e)$  realisieren, der folgender Übergangstabelle genügt:

| $C_e$ | Q | $Q_{n+1}$        |

|-------|---|------------------|

| 0     | 0 | 0                |

| 0     | 1 | 1                |

| 1     | 0 | $\overline{Q}_n$ |

| 1     | 1 | $\overline{Q}_n$ |

a) Vervollständigen Sie zuerst die Funktionstabelle des Schaltnetzes:

| T | Q | D |

|---|---|---|

| 0 | 0 |   |

| 0 | 1 |   |

| 1 | 0 |   |

| 1 | 1 |   |

- b) Wie lässt sich mit vier solcher 1-Bit-Zähler der synchrone 4-Bit-Zähler realisieren?

- c) Versuchen Sie eine Bedingung für Zustandswechsel (Toggle) der Zählerbits  $z_3, z_2, z_1, z_0$  zu formulieren. Schauen Sie sich dazu noch mal genau Zählen im Dualsystem an. Wann wechselt ein Zählerbit?